## NETWORK ALGORITHMICS

AN INTERDISCIPLINARY APPROACH TO DESIGNING FAST NETWORKED DEVICES

GEORGE VARGHESE

**Network Algorithmics**

#### The Morgan Kaufmann Series in Networking

#### Series Editor, David Clark, M.I.T.

Network Algorithmics: An Interdisciplinary Approach to Designing Fast Networked Devices George Varghese

Network Recovery: Protection and Restoration of Optical, SONET-SDH, IP, and MPLS Jean Philippe Vasseur, Mario Pickavet, and Piet Demeester

Routing, Flow, and Capacity Design in Communication and Computer Networks Michal Pióro and Deepankar Medhi

Wireless Sensor Networks: An Information Processing Approach Feng Zhao and Leonidas Guibas

*Communication Networking: An Analytical Approach* Anurag Kumar, D. Manjunath, and Joy Kuri

The Internet and Its Protocols: A Comparative Approach Adrian Farrel

Modern Cable Television Technology: Video, Voice, and Data Communications, 2e Walter Ciciora, James Farmer, David Large, and Michael Adams

Bluetooth Application Programming with the Java APIs C. Bala Kumar, Paul J. Kline, and Timothy J. Thompson

Policy-Based Network Management: Solutions for the Next Generation John Strassner

*Computer Networks: A Systems Approach,* 3e Larry L. Peterson and Bruce S. Davie

*Network Architecture, Analysis, and Design,* 2e James D. McCabe

MPLS Network Management: MIBs, Tools, and Techniques Thomas D. Nadeau

Developing IP-Based Services: Solutions for Service Providers and Vendors Monique Morrow and Kateel Vijayananda

*Telecommunications Law in the Internet Age* Sharon K. Black *Optical Networks: A Practical Perspective,* 2e Rajiv Ramaswami and Kumar N. Sivarajan

Internet QoS: Architectures and Mechanisms Zheng Wang

TCP/IP Sockets in Java: Practical Guide for Programmers Michael J. Donahoo and Kenneth L. Calvert

TCP/IP Sockets in C: Practical Guide for Programmers Kenneth L. Calvert and Michael J. Donahoo

Multicast Communication: Protocols, Programming, and Applications Ralph Wittmann and Martina Zitterbart

MPLS: Technology and Applications Bruce Davie and Yakov Rekhter

High-Performance Communication Networks, 2e Jean Walrand and Pravin Varaiya

Internetworking Multimedia Jon Crowcroft, Mark Handley, and Ian Wakeman

Understanding Networked Applications: A First Course David G. Messerschmitt

Integrated Management of Networked Systems: Concepts, Architectures, and Their Operational Applications Heinz-Gerd Hegering. Sebastian Abeck, and Bernhard Neumair

Virtual Private Networks: Making the Right Connection Dennis Fowler

Networked Applications: A Guide to the New Computing Infrastructure David G. Messerschmitt

Wide Area Network Design: Concepts and Tools for Optimization Robert S. Cahn

For further information on these books and for a list of forthcoming titles, please visit our website at http://www.mkp.com.

# **Network Algorithmics**

An Interdisciplinary Approach to Designing Fast Networked Devices

**George Varghese** *University of California, San Diego*

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

MORGAN KAUFMANN PUBLISHERS IS AN IMPRINT OF ELSEVIER

Elsevier/Morgan Kaufmann Publishing Director: Diane D. Cerra Senior Acquisitions Editor: Rick Adams Associate Editor: Karyn Johnson Editorial Coordinator: Mona Buehler Publishing Services Manager: Simon Crump Senior Project Manager: Angela Dooley Cover Design Manager: Cate Rickard Barr Cover Design: Yvo Riezebos Design

Morgan Kaufmann is an imprint of Elsevier. 500 Sansome Street, Suite 400, San Francisco, CA 94111

This book is printed on acid-free paper.

© 2005 by Elsevier Inc.

Designations used by companies to distinguish their products are often claimed as trademarks or registered trademarks. In all instances in which Elsevier is aware of a claim, the product names appear in initial capital or all capital letters. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means electronic, mechanical, photocopying, scanning, or otherwise without prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com) by selecting "Customer Support" and then "Obtaining Permissions."

Library of Congress Cataloging-in-Publication Data Application submitted

ISBN: 0-12-088477-1

For information on all Morgan Kaufmann publications, visit our website at www.mkp.com.

Printed in the United States of America 08 07 06 05 04 5 4 3 2 1

Cover Image: Getty Images Text Design: Michael Remener Composition: CEPHA Technical Illustration: Dartmouth Publishing, Inc. Copyeditor: Elliot Simon Proofreader: Phyllis Coyne et al. Indexer: Northwind Editorial Interior Printer: The Maple-Vail Book Manufacturing Group Cover Printer: Phoenix Color For Aju and Tim and Andrew, who made all this possible ...

## CONTENTS

3

PREFACE xix

## PART I The Rules of the Game 1 CHAPTER 1 Introducing Network Algorithmics 3

#### 1.1 The Problem: Network Bottlenecks

- 1.1.1 Endnode Bottlenecks 4

- 1.1.2 Router Bottlenecks 5

#### 1.2 The Techniques: Network Algorithmics 7

- 1.2.1 Warm-up Example: Scenting an Evil Packet 8

- 1.2.2 Strawman Solution 9

- 1.2.3 Thinking Algorithmically 9

- 1.2.4 Refining the Algorithm: Exploiting Hardware 10

- 1.2.5 Cleaning Up 11

- 1.2.6 Characteristics of Network Algorithmics 13

- 1.3 Exercise 15

#### **CHAPTER 2** Network Implementation Models 16

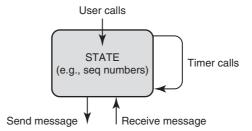

#### 2.1 Protocols 17

- 2.1.1 Transport and Routing Protocols 17

- 2.1.2 Abstract Protocol Model 17

- 2.1.3 Performance Environment and Measures 19

#### 2.2 Hardware 21

- 2.2.1 Combinatorial Logic 21

- 2.2.2 Timing and Power 22

| 2.2.3 | Raising the Abstraction Level of Hardware Design | 23 |

|-------|--------------------------------------------------|----|

|       |                                                  |    |

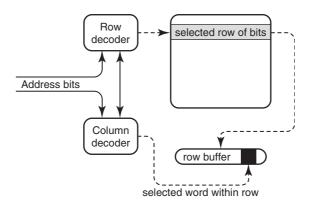

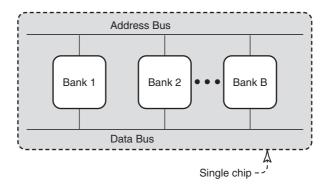

- 2.2.4 Memories 25

- 2.2.5 Memory Subsystem Design Techniques 29

- 2.2.6 Component-Level Design 30

- 2.2.7 Final Hardware Lessons 31

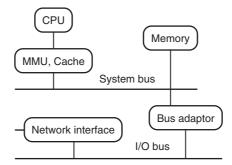

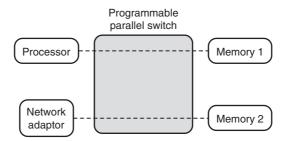

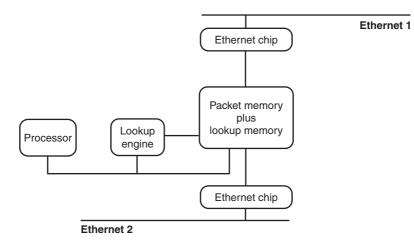

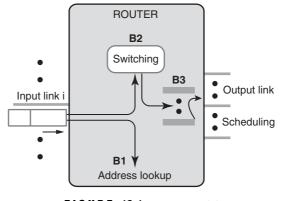

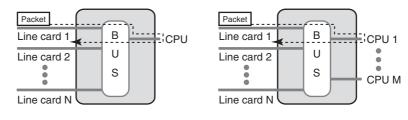

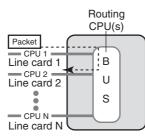

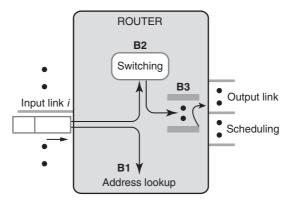

#### 2.3 Network Device Architectures 32

- 2.3.1 Endnode Architecture 32

- 2.3.2 Router Architecture 34

#### 2.4 Operating Systems 39

- 2.4.1 Uninterrupted Computation via Processes 39

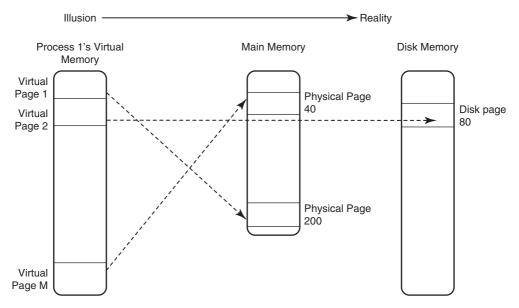

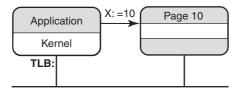

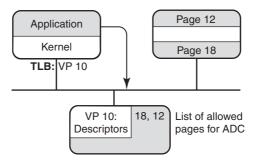

- 2.4.2 Infinite Memory via Virtual Memory 41

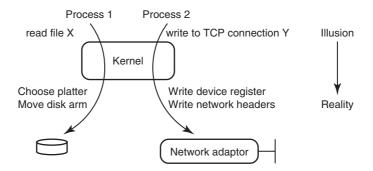

- 2.4.3 Simple I/O via System Calls 43

- 2.5 Summary 44

- 2.6 Exercises 44

#### **CHAPTER 3** Fifteen Implementation Principles 50

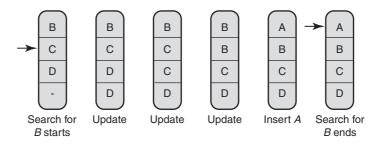

- 3.1 Motivating the Use of Principles Updating Ternary Content-Addressable Memories 50

- 3.2 Algorithms versus Algorithmics 54

- 3.3 Fifteen Implementation Principles Categorization and Description 56

- 3.3.1 Systems Principles 56

- 3.3.2 Principles for Modularity with Efficiency 61

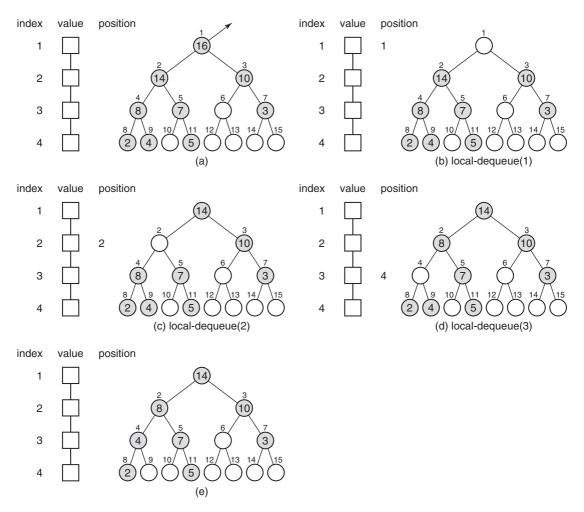

- 3.3.3 Principles for Speeding Up Routines 63

- 3.4 Design versus Implementation Principles 65

#### 3.5 Caveats 66

- 3.5.1 Eight Cautionary Questions 68

- 3.6 Summary 70

- 3.7 Exercises 70

#### CHAPTER 4 Principles in Action 73

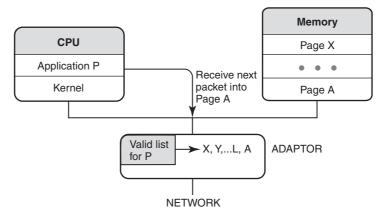

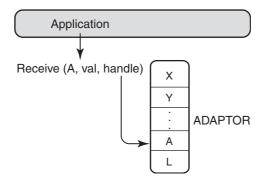

| 4.1 | Buffer Validation of Application Device Channels | 74 |

|-----|--------------------------------------------------|----|

|-----|--------------------------------------------------|----|

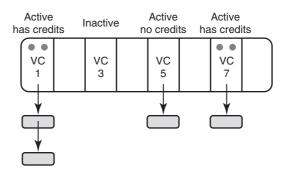

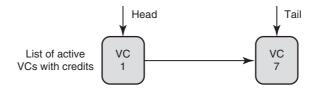

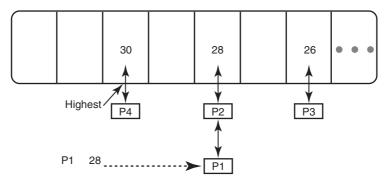

- 4.2 Scheduler for Asynchronous Transfer Mode Flow Control 76

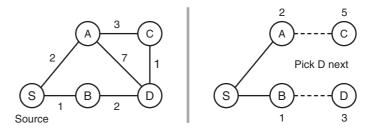

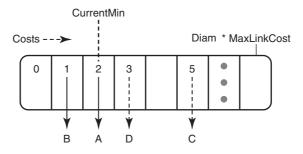

- 4.3 Route Computation Using Dijkstra's Algorithm 77

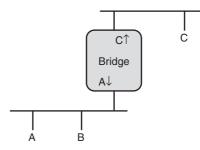

- 4.4 Ethernet Monitor Using Bridge Hardware 80

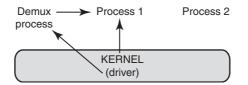

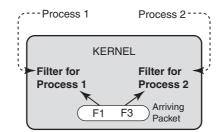

| 4.5  | Demultiplexing in the X-Kernel 81                     |

|------|-------------------------------------------------------|

| 4.6  | Tries with Node Compression 83                        |

| 4.7  | Packet Filtering in Routers 85                        |

| 4.8  | Avoiding Fragmentation of Link State Packets 87       |

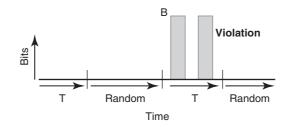

| 4.9  | Policing Traffic Patterns 90                          |

| 4.10 | Identifying a Resource Hog 92                         |

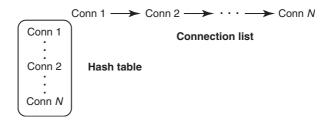

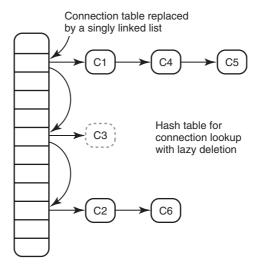

| 4.11 | Getting Rid of the TCP Open Connection List 93        |

| 4.12 | Acknowledgment Withholding 96                         |

| 4.13 | Incrementally Reading a Large Database 98             |

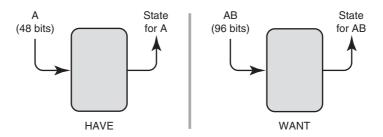

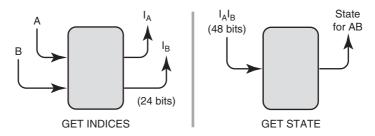

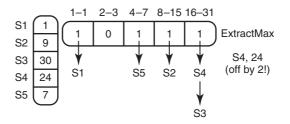

| 4.14 | Binary Search of Long Identifiers 100                 |

| 4.15 | Video Conferencing via Asynchronous Transfer Mode 102 |

## PART II Playing with Endnodes 105

### CHAPTER 5 Copying Data 107

| 5.1 | Why D  | ata Copies 109                                   |

|-----|--------|--------------------------------------------------|

| 5.2 | Reduci | ing Copying via Local Restructuring 111          |

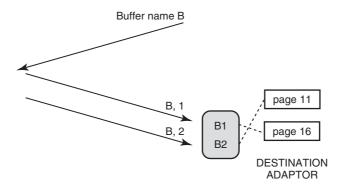

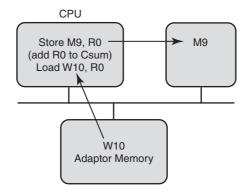

|     | 5.2.1  | Exploiting Adaptor Memory 111                    |

|     | 5.2.2  | Using Copy-on-Write 113                          |

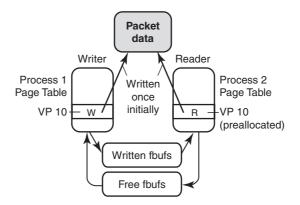

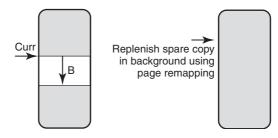

|     | 5.2.3  | Fbufs: Optimizing Page Remapping 115             |

|     | 5.2.4  | Transparently Emulating Copy Semantics 119       |

| 5.3 | Avoidi | ng Copying Using Remote DMA 121                  |

|     | 5.3.1  | Avoiding Copying in a Cluster 122                |

|     | 5.3.2  | Modern-Day Incarnations of RDMA 123              |

| 5.4 | Broade | ening to File Systems 125                        |

|     | 5.4.1  | Shared Memory 125                                |

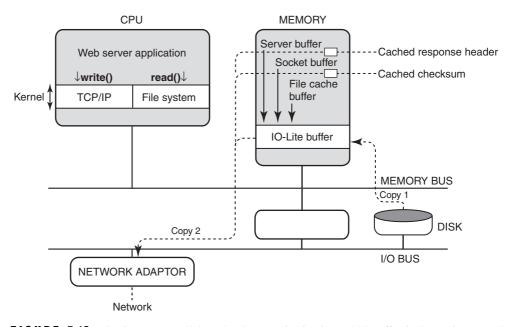

|     | 5.4.2  | IO-Lite: A Unified View of Buffering 126         |

|     | 5.4.3  | Avoiding File System Copies via I/O Splicing 128 |

| 5.5 | Broade | ening beyond Copies 129                          |

| 5.6 | Broade | ening beyond Data Manipulations 131              |

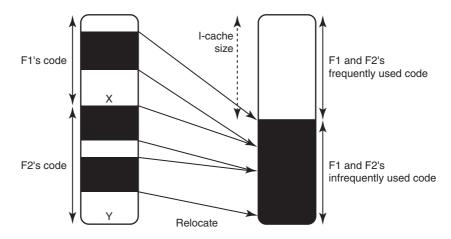

|     | 5.6.1  | Using Caches Effectively 131                     |

|     | 5.6.2  | Direct Memory Access versus Programmed I/O 135   |

| 5.7       | Conclusions 135                                                |

|-----------|----------------------------------------------------------------|

| 5.8       | Exercises 137                                                  |

| 0 U A D T | F.D.C. Transforming Control 120                                |

| CHAPT     | 0                                                              |

| 6.1       | Why Control Overhead? 141                                      |

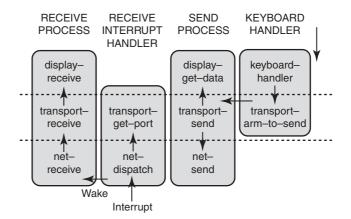

| 6.2       | Avoiding Scheduling Overhead in Networking Code 143            |

|           | 6.2.1 Making User-Level Protocol Implementations Real 144      |

| 6.3       | Avoiding Context-Switching Overhead in Applications 146        |

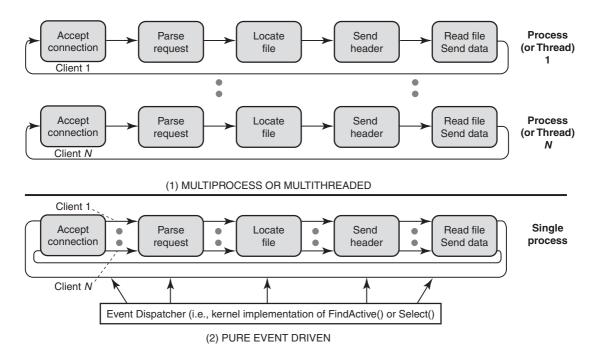

|           | 6.3.1 Process per Client 147                                   |

|           | 6.3.2 Thread per Client 148                                    |

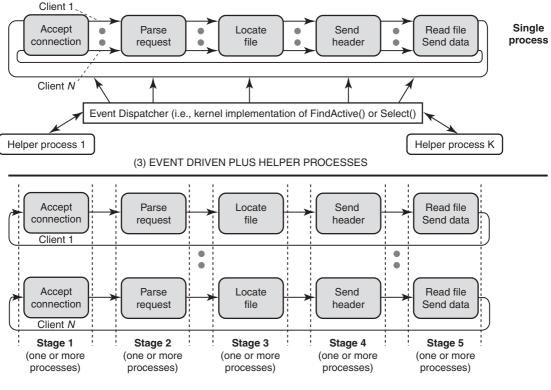

|           | 6.3.3 Event-Driven Scheduler 150                               |

|           | 6.3.4 Event-Driven Server with Helper Processes 150            |

|           | 6.3.5 Task-Based Structuring 151                               |

| 6.4       | Fast Select 153                                                |

|           | 6.4.1 A Server Mystery 153                                     |

|           | 6.4.2 Existing Use and Implementation of <i>Select()</i> 154   |

|           | 6.4.3 Analysis of Select() 155                                 |

|           | 6.4.4 Speeding Up <i>Select()</i> without Changing the API 157 |

|           | 6.4.5 Speeding Up <i>Select()</i> by Changing the API 158      |

| 6.5       | Avoiding System Calls 159                                      |

|           | 6.5.1 The Virtual Interface Architecture (VIA) Proposal 162    |

| 6.6       | Reducing Interrupts 163                                        |

|           | 6.6.1 Avoiding Receiver Livelock 164                           |

| 6.7       | Conclusions 165                                                |

| 6.8       | Exercises 166                                                  |

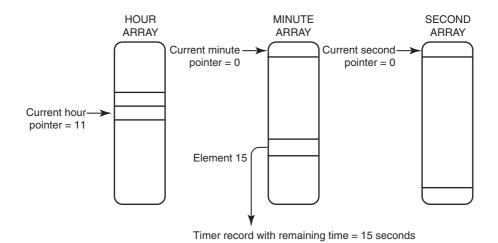

| CHAPT     | ER 7 Maintaining Timers 169                                    |

| 7.1       | Why Timers? 169                                                |

| 7.2       | Model and Performance Measures 171                             |

| 7.3       | Simplest Timer Schemes 172                                     |

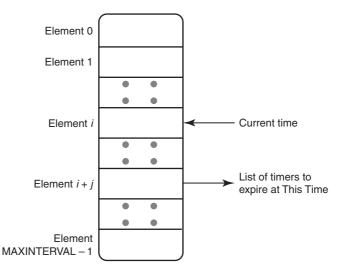

- 7.4 Timing Wheels 173

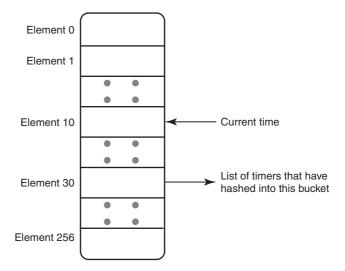

- 7.5 Hashed Wheels 175

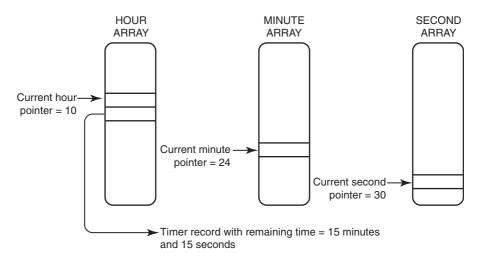

- 7.6 Hierarchical Wheels 176

- 7.7 BSD Implementation 178

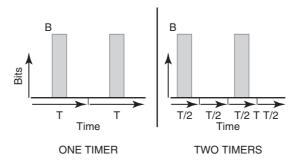

- 7.8 Obtaining Fine-Granularity Timers 179

- 7.9 Conclusions 180

- 7.10 Exercises 181

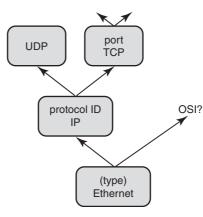

#### CHAPTER 8 Demultiplexing 182

| 8.1 Op | portunities and | Challenges | of Early | / Demultiplexing | 184 |

|--------|-----------------|------------|----------|------------------|-----|

|--------|-----------------|------------|----------|------------------|-----|

- 8.2 Goals 184

- 8.3 CMU/Stanford Packet Filter: Pioneering Packet Filters 185

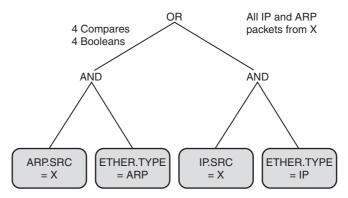

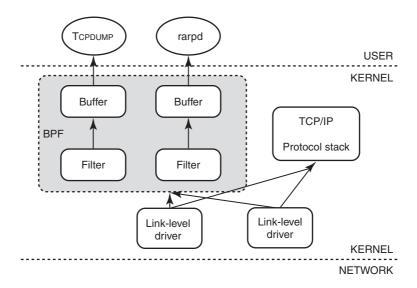

- 8.4 Berkeley Packet Filter: Enabling High-Performance Monitoring 186

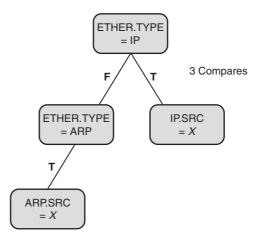

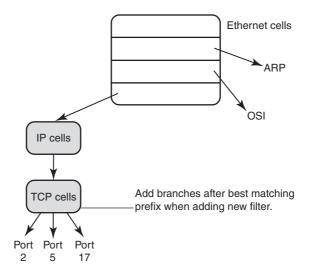

- 8.5 Pathfinder: Factoring Out Common Checks 189

- 8.6 Dynamic Packet Filter: Compilers to the Rescue 192

- 8.7 Conclusions 195

- 8.8 Exercises 195

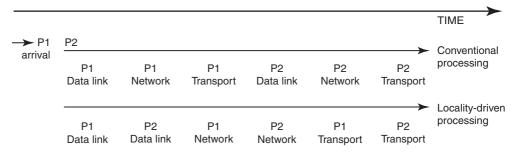

#### CHAPTER 9 Protocol Processing 197

#### 9.1 Buffer Management 198

- 9.1.1 Buffer Allocation 199

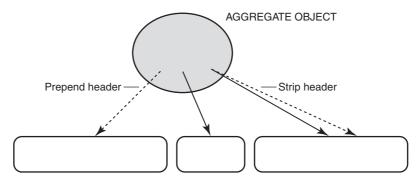

- 9.1.2 Sharing Buffers 201

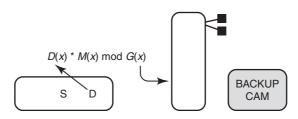

#### 9.2 Cyclic Redundancy Checks and Checksums 203

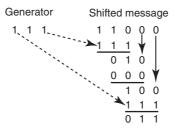

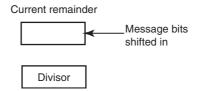

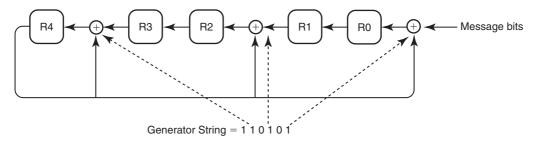

- 9.2.1 Cyclic Redundancy Checks 204

- 9.2.2 Internet Checksums 207

- 9.2.3 Finessing Checksums 209

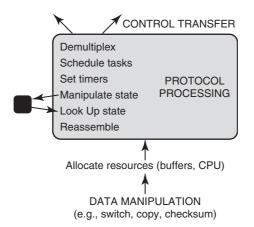

- 9.3 Generic Protocol Processing 209

- 9.3.1 UDP Processing 212

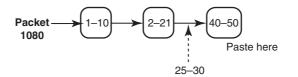

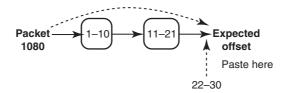

- 9.4 Reassembly 213

- 9.4.1 Efficient Reassembly 214

- 9.5 Conclusions 216

- 9.6 Exercises 217

#### PART III Playing with Routers 219

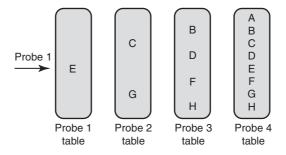

#### CHAPTER 10 Exact-Match Lookups 221

10.1 Challenge 1: Ethernet under Fire 222

| 10.2  | Challenge 2: Wire Speed Forwarding 224                                                   |

|-------|------------------------------------------------------------------------------------------|

| 10.3  | Challenge 3: Scaling Lookups to Higher Speeds 228                                        |

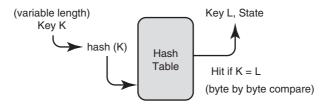

| 1010  | 10.3.1 Scaling via Hashing 228                                                           |

|       | 10.3.2 Using Hardware Parallelism 230                                                    |

| 10.4  | Summary 231                                                                              |

| 10.5  | Exercise 232                                                                             |

| CHAPT | E R 1 1 Prefix-Match Lookups 233                                                         |

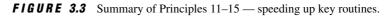

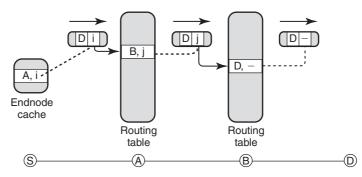

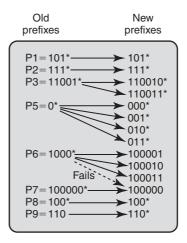

| 11.1  | Introduction to Prefix Lookups 234                                                       |

|       | 11.1.1 Prefix Notation 234                                                               |

|       | 11.1.2 Why Variable-Length Prefixes? 235                                                 |

|       | 11.1.3 Lookup Model 236                                                                  |

| 11.2  | Finessing Lookups 238                                                                    |

|       | 11.2.1 Threaded Indices and Tag Switching 238                                            |

|       | 11.2.2 Flow Switching 240                                                                |

|       | 11.2.3 Status of Tag Switching, Flow Switching, and Multiprotocol<br>Label Switching 241 |

| 11.3  | Nonalgorithmic Techniques for Prefix Matching 242                                        |

|       | 11.3.1 Caching 242                                                                       |

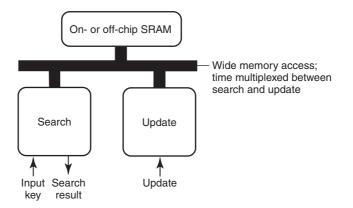

|       | 11.3.2 Ternary Content-Addressable Memories 242                                          |

| 11.4  | Unibit Tries 243                                                                         |

| 11.5  | Multibit Tries 245                                                                       |

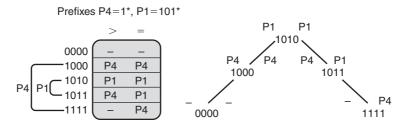

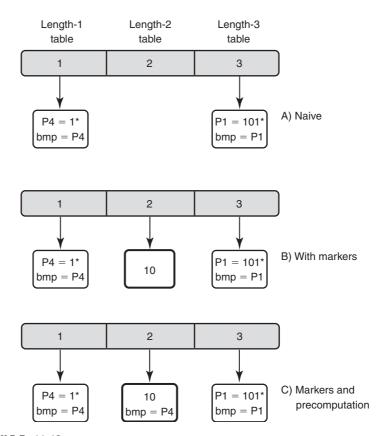

|       | 11.5.1 Fixed-Stride Tries 246                                                            |

|       | 11.5.2 Variable-Stride Tries 247                                                         |

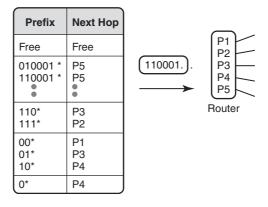

|       | 11.5.3 Incremental Update 250                                                            |

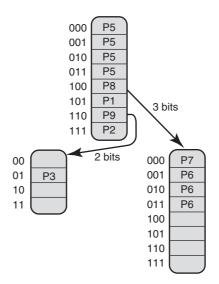

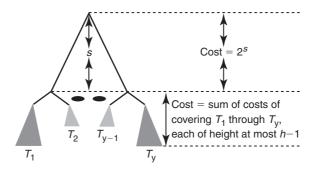

| 11.6  | Level-Compressed (LC) Tries 250                                                          |

| 11.7  | Lulea-Compressed Tries 252                                                               |

| 11.8  | Tree Bitmap 255                                                                          |

|       | 11.8.1 Tree Bitmap Ideas 255                                                             |

|       | 11.8.2Tree Bitmap Search Algorithm256                                                    |

| 11.9  | Binary Search on Ranges 257                                                              |

| 11.10 | Binary Search on Prefix Lengths 259                                                      |

| 11.11 | Memory Allocation in Compressed Schemes 261                                              |

|       | 11.11.1 Frame-Based Compaction 262                                                       |

286

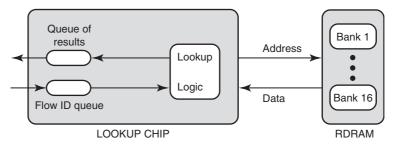

- 11.12 Lookup-Chip Model 263

- 11.13 Conclusions 265

- 11.14 Exercises 266

#### CHAPTER 12 Packet Classification 270

| 12.1  | Why Packet Classification? 271                    |   |

|-------|---------------------------------------------------|---|

| 12.2  | Packet-Classification Problem 273                 |   |

| 12.3  | Requirements and Metrics 275                      |   |

| 12.4  | Simple Solutions 276                              |   |

|       | 12.4.1 Linear Search 276                          |   |

|       | 12.4.2 Caching 276                                |   |

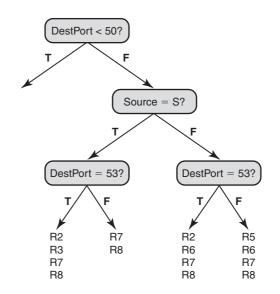

|       | 12.4.3 Demultiplexing Algorithms 277              |   |

|       | 12.4.4 Passing Labels 277                         |   |

|       | 12.4.5 Content-Addressable Memories 278           |   |

| 12.5  | Two-Dimensional Schemes 278                       |   |

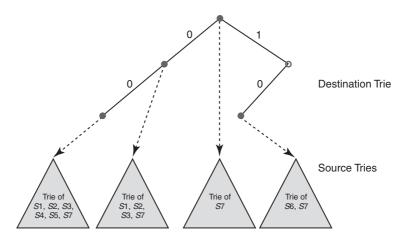

|       | 12.5.1 Fast Searching Using Set-Pruning Trees 278 |   |

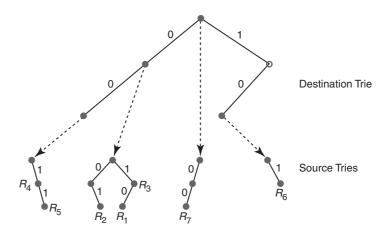

|       | 12.5.2 Reducing Memory Using Backtracking 281     |   |

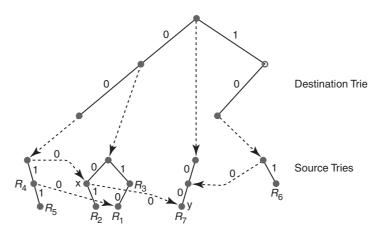

|       | 12.5.3 The Best of Both Worlds: Grid of Tries 281 |   |

| 12.6  | Approaches to General Rule Sets 284               |   |

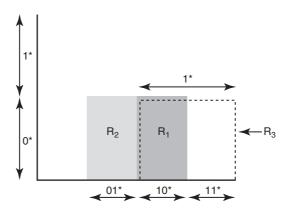

|       | 12.6.1 Geometric View of Classification 284       |   |

|       | 12.6.2 Beyond Two Dimensions: The Bad News 28     | 6 |

|       | 12.6.3 Beyond Two Dimensions: The Good News 2     | 8 |

| 12.7  | Extending Two-Dimensional Schemes 287             |   |

| 12.8  | Using Divide-and-Conquer 288                      |   |

| 12.9  | Bit Vector Linear Search 289                      |   |

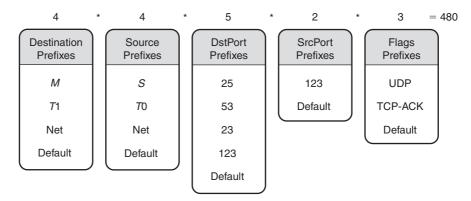

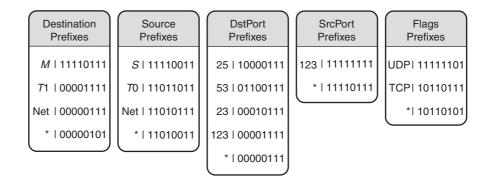

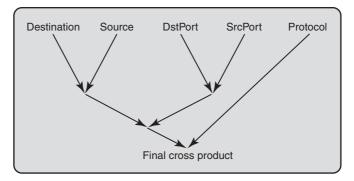

| 12.10 | Cross-Producting 292                              |   |

| 12.11 | Equivalenced Cross-Producting 293                 |   |

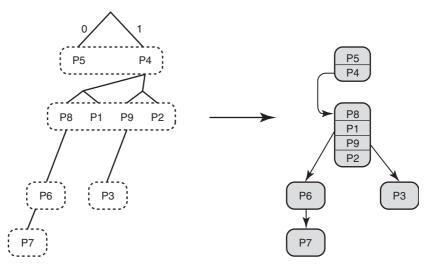

| 12.12 | Decision Tree Approaches 296                      |   |

| 12.13 | Conclusions 299                                   |   |

| 12.14 | Exercises 300                                     |   |

| CHAPT | ER 13 Switching 302                               |   |

**13.1** Router versus Telephone Switches 304

| 13.2  | Shared-Memory Switches 305                                                 |  |  |

|-------|----------------------------------------------------------------------------|--|--|

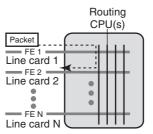

| 13.3  | Router History: From Buses to Crossbars 305                                |  |  |

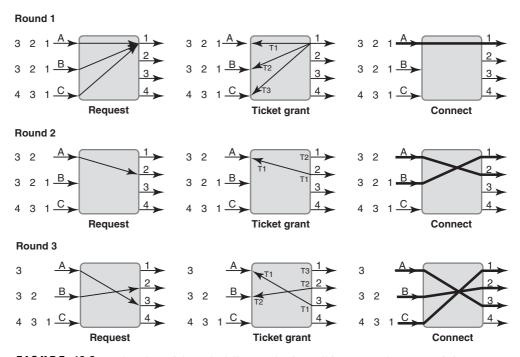

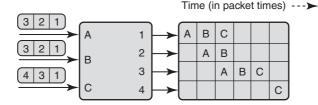

| 13.4  | The Take-a-Ticket Crossbar Scheduler 307                                   |  |  |

| 13.5  | Head-of-Line Blocking 311                                                  |  |  |

| 13.6  | Avoiding Head-of-Line Blocking via Output Queuing 312                      |  |  |

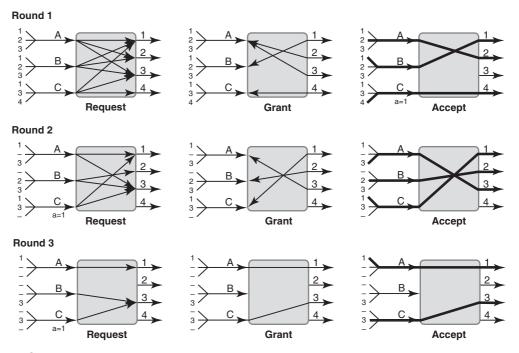

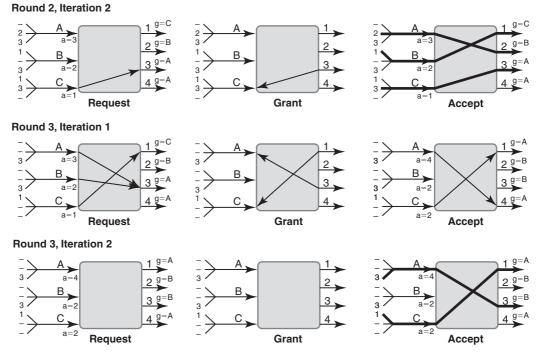

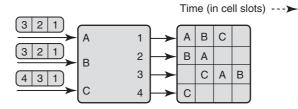

| 13.7  | Avoiding Head-of-Line Blocking by Using Parallel Iterative<br>Matching 314 |  |  |

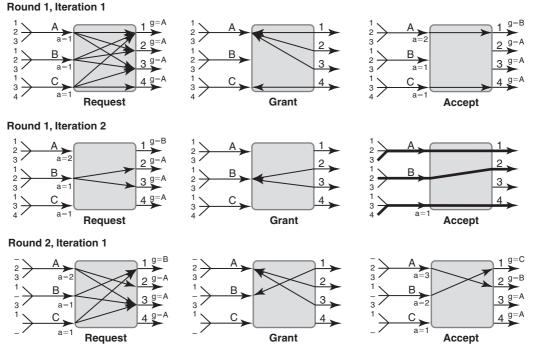

| 13.8  | Avoiding Randomization with iSLIP 316                                      |  |  |

|       | 13.8.1 Extending iSLIP to Multicast and Priority 320                       |  |  |

|       | 13.8.2 iSLIP Implementation Notes 322                                      |  |  |

| 13.9  | Scaling to Larger Switches 323                                             |  |  |

|       | 13.9.1 Measuring Switch Cost 324                                           |  |  |

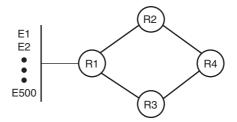

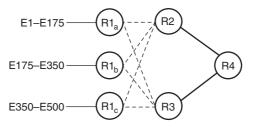

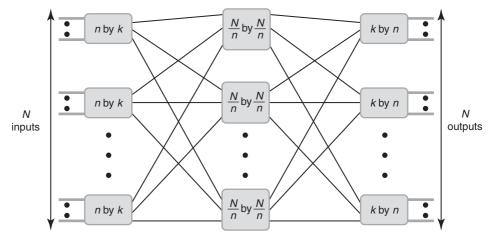

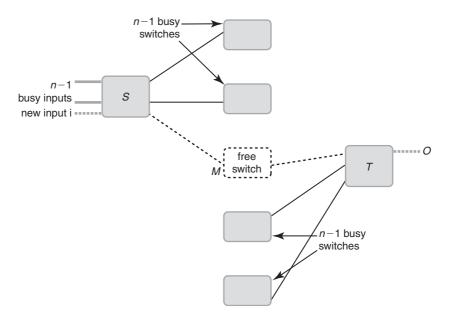

|       | 13.9.2Clos Networks for Medium-Size Routers324                             |  |  |

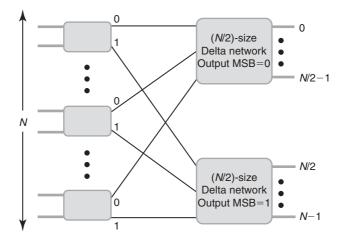

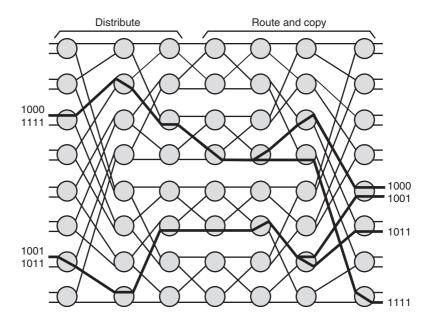

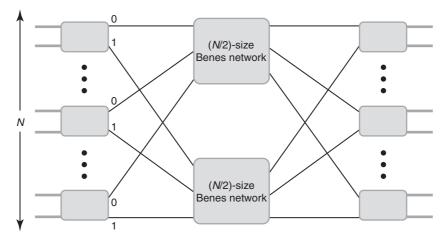

|       | 13.9.3Benes Networks for Larger Routers328                                 |  |  |

| 13.10 | Scaling to Faster Switches 333                                             |  |  |

|       | 13.10.1 Using Bit Slicing for Higher-Speed Fabrics333                      |  |  |

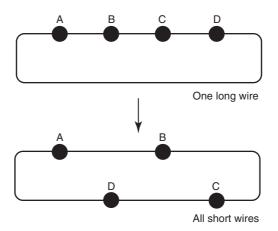

|       | 13.10.2 Using Short Links for Higher-Speed Fabrics 334                     |  |  |

|       | 13.10.3 Memory Scaling Using Randomization335                              |  |  |

| 13.11 | Conclusions 336                                                            |  |  |

| 13.12 | Exercises 337                                                              |  |  |

| CHAPT | T E R 1 4 Scheduling Packets 339                                           |  |  |

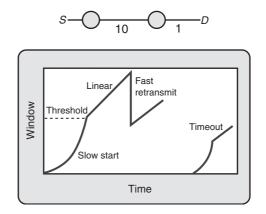

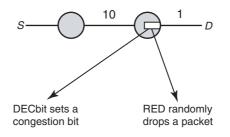

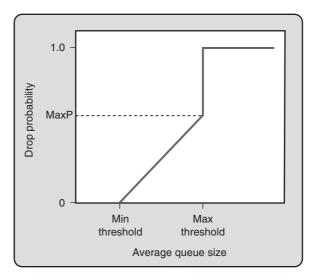

| 14.1  | Motivation for Quality of Service 340                                      |  |  |

| 14.2  | Random Early Detection 342                                                 |  |  |

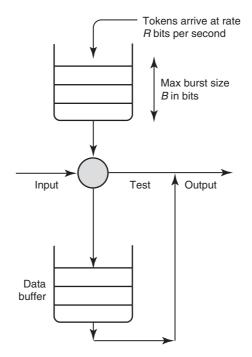

| 14.3  | Token Bucket Policing 345                                                  |  |  |

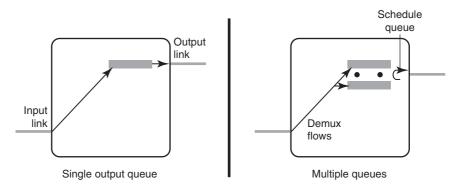

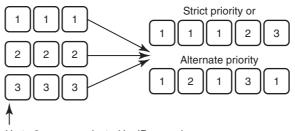

| 14.4  | Multiple Outbound Queues and Priority 346                                  |  |  |

| 14.5  | A Quick Detour into Reservation Protocols 347                              |  |  |

| 14.6  | Providing Bandwidth Guarantees 348                                         |  |  |

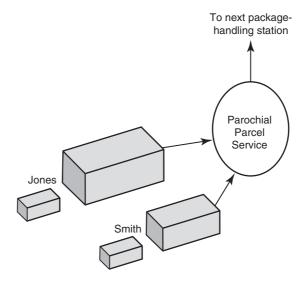

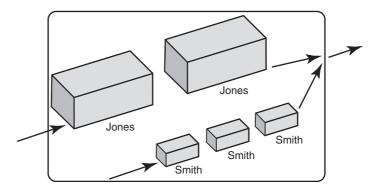

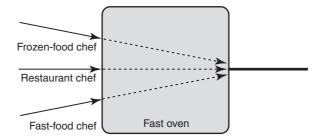

|       | 14.6.1 The Parochial Parcel Service 348                                    |  |  |

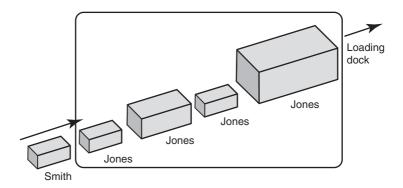

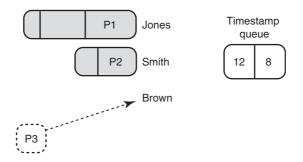

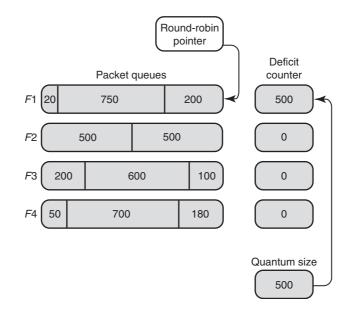

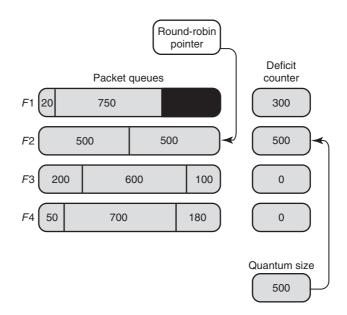

|       | 14.6.2 Deficit Round-Robin 350                                             |  |  |

|       | 14.6.3 Implementation and Extensions of Deficit Round-Robin                |  |  |

| 14.7  | Schedulers That Provide Delay Guarantees 354                               |  |  |

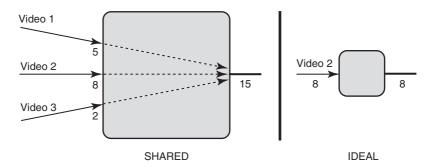

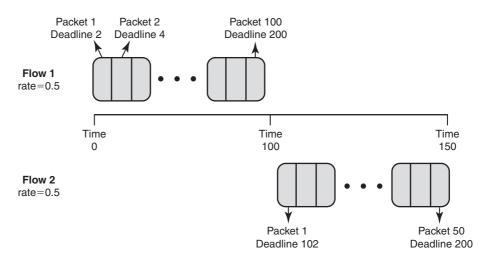

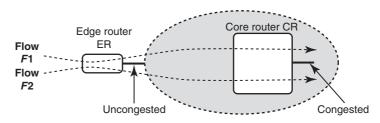

| 14.8  | Scalable Fair Queuing 358                                                  |  |  |

|       | 14.8.1 Random Aggregation 359                                              |  |  |

351

*362*

|       | 14.8.2Edge Aggregation35914.8.3Edge Aggregation with Policing360 |

|-------|------------------------------------------------------------------|

| 44.0  |                                                                  |

| 14.9  | Summary 361                                                      |

| 14.10 | Exercises 361                                                    |

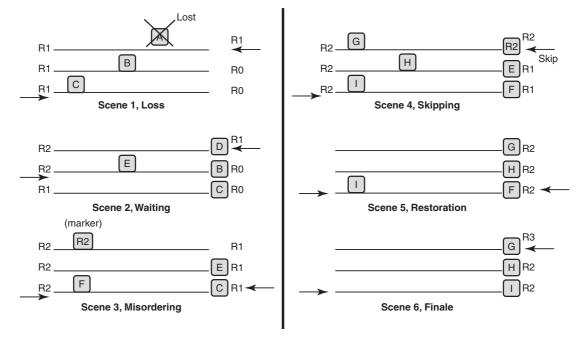

| CHAPT | ER 15 Routers as Distributed Systems                             |

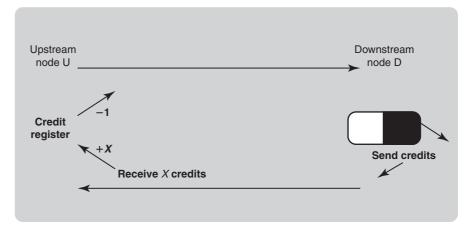

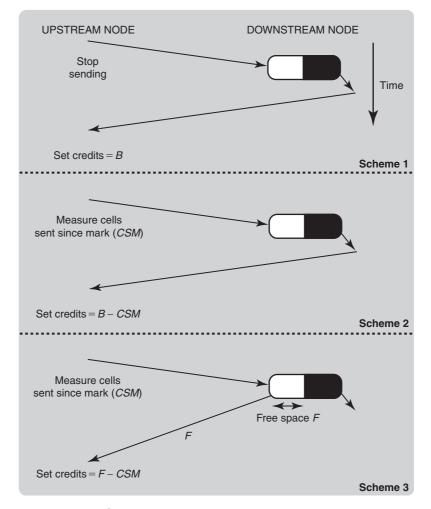

| 15.1  | Internal Flow Control 363                                        |

|       | 15.1.1 Improving Performance 364                                 |

|       | 15.1.2 Rescuing Reliability 365                                  |

| 15.2  | Internal Striping 368                                            |

|       | 15.2.1 Improving Performance 368                                 |

|       | 15.2.2 Rescuing Reliability 369                                  |

| 15.3  | Asynchronous Updates 371                                         |

|       | 15.3.1 Improving Performance 372                                 |

|       | 15.3.2 Rescuing Reliability 373                                  |

| 15.4  | Conclusions 373                                                  |

| 15.5  | Exercises 374                                                    |

## PART IV Endgame 377

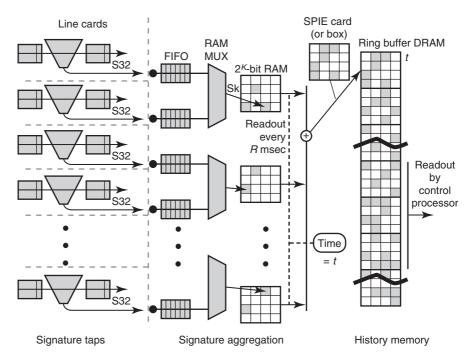

### CHAPTER 16 Measuring Network Traffic 379

| 16.1  | Why Measurement Is Hard 381                            |

|-------|--------------------------------------------------------|

|       | 16.1.1 Why Counting Is Hard 381                        |

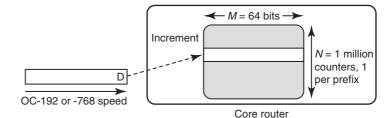

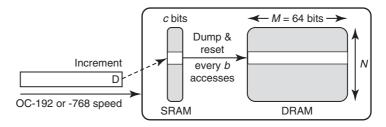

| 16.2  | Reducing SRAM Width Using DRAM Backing Store 382       |

| 16.3  | Reducing Counter Width Using Randomized Counting 384   |

| 16.4  | Reducing Counters Using Threshold Aggregation 385      |

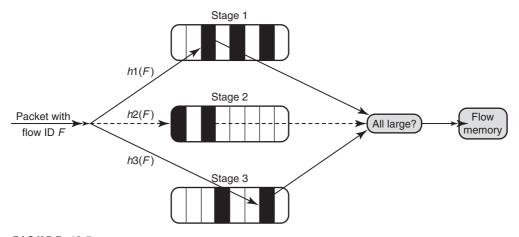

| 16.5  | Reducing Counters Using Flow Counting 387              |

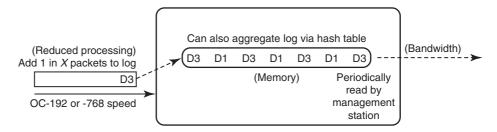

| 16.6  | Reducing Processing Using Sampled NetFlow 388          |

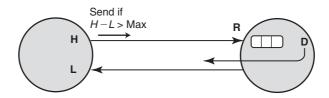

| 16.7  | Reducing Reporting Using Sampled Charging 389          |

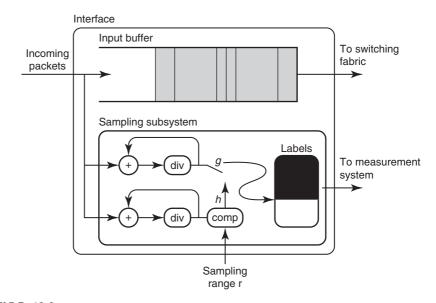

| 16.8  | Correlating Measurements Using Trajectory Sampling 390 |

| 16.9  | A Concerted Approach to Accounting 392                 |

| 16.10 | Computing Traffic Matrices 393                         |

16.10.1 Approach 1: Internet Tomography 394

|       | 16.10.2 Approach 2: Per-Prefix Counters 394                              |

|-------|--------------------------------------------------------------------------|

|       | 16.10.3 Approach 3: Class Counters395                                    |

| 16.11 | Sting as an Example of Passive Measurement 395                           |

| 16.12 | Conclusion 396                                                           |

| 16.13 | Exercises 397                                                            |

| CHAPT | E R 1 7 Network Security 399                                             |

| 17.1  | Searching for Multiple Strings in Packet Payloads 401                    |

|       | 17.1.1 Integrated String Matching Using Aho–Corasick 402                 |

|       | 17.1.2 Integrated String Matching Using Boyer–Moore 403                  |

| 17.2  | Approximate String Matching 405                                          |

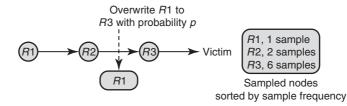

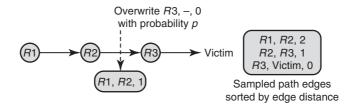

| 17.3  | IP Traceback via Probabilistic Marking 406                               |

| 17.4  | IP Traceback via Logging 409                                             |

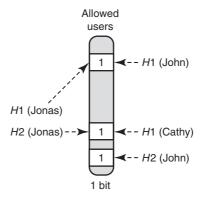

|       | 17.4.1 Bloom Filters 410                                                 |

|       | 17.4.2 Bloom Filter Implementation of Packet Logging 412                 |

| 17.5  | Detecting Worms 413                                                      |

| 17.6  | Conclusion 415                                                           |

| 17.7  | Exercises 415                                                            |

| снлрт | ER 18 Conclusions 417                                                    |

|       |                                                                          |

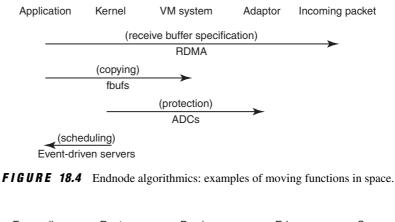

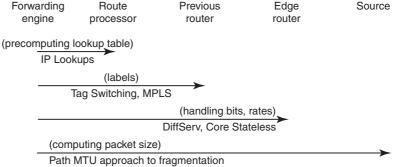

| 18.1  | What This Book Has Been About41818.1.1Endnode Algorithmics418            |

|       | 18.1.1Endnode Algorithmics41818.1.2Router Algorithmics419                |

|       | 18.1.3 Toward a Synthesis 420                                            |

| 18.2  | ·                                                                        |

| 10.2  | What Network Algorithmics Is About42318.2.1Interdisciplinary Thinking423 |

|       | 18.2.2 Systems Thinking 424                                              |

|       | 18.2.3 Algorithmic Thinking 425                                          |

| 18.3  | Network Algorithmics and Real Products 427                               |

|       | •                                                                        |

| 18.4  | Network Algorithmics: Back to the Future 429                             |

|       | 18.4.1 New Abstractions 429                                              |

|       | 18.4.2New Connecting Disciplines43018.4.3New Requirements431             |

|       | 1                                                                        |

| 18.5  | The Inner Life of a Networking Device 431                                |

#### APPENDIX Detailed Models 433

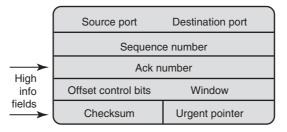

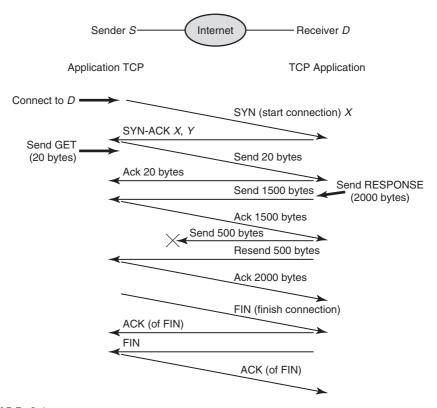

#### A.1 TCP and IP 433

- A.1.1 Transport Protocols 433

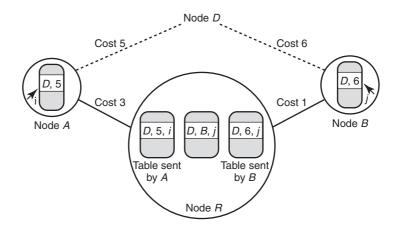

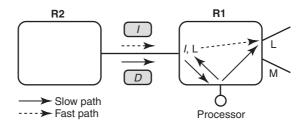

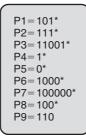

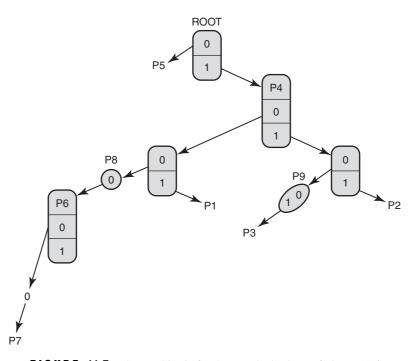

- A.1.2 Routing Protocols 436

#### A.2 Hardware Models 437

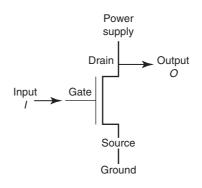

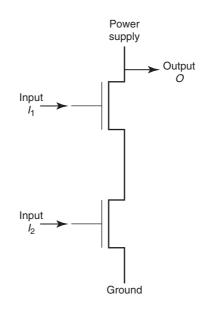

- A.2.1 From Transistors to Logic Gates 437

- A.2.2 Timing Delays 439

- A.2.3 Hardware Design Building Blocks 439

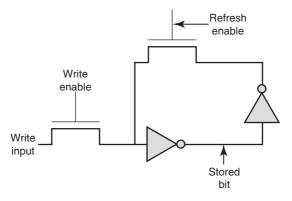

- A.2.4 Memories: The Inside Scoop 440

- A.2.5 Chip Design 441

#### A.3 Switching Theory 442

A.3.1 Matching Algorithms for Clos Networks with k = n 442

A.4 The Interconnection Network Zoo 443

#### Bibliography 445

Index 457

## PREFACE

Computer networks have become an integral part of society. We take for granted the ability to transact commerce over the Internet and that users can avail themselves of a burgeoning set of communication methods, which range from file sharing to Web logs. However, for networks to take their place as part of the fundamental infrastructure of society, they must provide performance guarantees.

We take for granted that electricity will flow when a switch is flicked and that telephone calls will be routed on Mother's Day. But the performance of computer networks such as the Internet is still notoriously unreliable. While there are many factors that go into performance, one major issue is that of network bottlenecks. There are two types of network bottlenecks: *resource bottlenecks* and *implementation bottlenecks*.

Resource bottlenecks occur when network performance is limited by the speed of the underlying hardware; examples include slow processors in server platforms and slow communication links. Resource bottlenecks can be worked around, at some cost, by buying faster hardware. However, it is quite often the case that the underlying hardware is perfectly adequate but that the real bottleneck is a design issue in the implementation. For example, a Web server running on the fastest processors may run slowly because of redundant data copying. Similarly, a router with a simple packet classification algorithm may start dropping packets when the number of ACL rules grows beyond a limit, though it keeps up with link speeds when classification is turned off. This book concentrates on such network implementation bottlenecks, especially at servers and routers.

Beyond servers and routers, new breeds of networking devices that introduce new performance bottlenecks are becoming popular. As networks become more integrated, devices such as storage area networks (SANs) and multimedia switches are becoming common. Further, as networks get more complex, various special-purpose network appliances for file systems and security are proliferating. While the first generation of such devices justified themselves by the new functions they provided, it is becoming critical that future network appliances keep up with link speeds.

Thus the objective of this book is to provide a set of techniques to overcome implementation bottlenecks at *all* networking devices and to provide a set of principles and models to help overcome current and *future* networking bottlenecks.

#### AUDIENCE

This book was written to answer a need for a text on efficient protocol implementations. The vast majority of networking books are on network protocols; even the implementation books are, for the most part, detailed explanations of the protocol. While protocols form the foundation of the field, there are just a handful of fundamental network infrastucture protocols left, such as TCP and IP. On the other hand, there are many implementations as most companies and start-ups customize their products to gain competitive advantage. This is exacerbated by the tendency to place TCP and IP everywhere, from bridges to SAN switches to toasters.

Thus there are many more people implementing protocols than designing them. *This is a textbook for implementors, networking students, and networking researchers, covering ground from the art of building a fast Web server to building a fast router and beyond.*

To do so, this book describes a collection of efficient implementation techniques; in fact, an initial section of each chapter concludes with a Quick Reference Guide for implementors that points to the most useful techniques for each topic. However, the book goes further and distills a fundamental method of crafting solutions to new network bottlenecks that we call *network algorithmics*. This provides the reader tools to design different implementations for specific contexts and to deal with new bottlenecks that will undoubtedly arise in a changing world.

Here is a detailed profile of our intended audience.

- Network Protocol Implementors: This group includes implementors of endnode

networking stacks for large servers, PCs, and workstations and for network appliances. It

also includes implementors of classic network interconnection devices, such as routers,

bridges, switches, and gateways, as well as devices that monitor networks for measurement

and security purposes. It also includes implementors of storage area networks, distributed

computing infrastructures, multimedia switches and gateways, and other new networking

devices. This book can be especially useful for implementors in start-ups as well as in

established companies, for whom improved performance can provide an edge.

- Networking Students: Undergraduate and graduate students who have mastered the basics

of network protocols can use this book as a text that describes how protocols should be

implemented to improve performance, potentially an important aspect of their future jobs.

- *Instructors:* Instructors can use this book as a textbook for a one-semester course on network algorithmics.

- *Systems Researchers:* Networking and other systems researchers can use this text as a reference and as a stimulus for further research in improving system performance. Given that disributed operating systems and distributed computing infrastructures (e.g., the Grid) rely on an underlying networking core whose performance can be critical, this book can be useful to general systems researchers.

#### WHAT THIS BOOK IS ABOUT

Chapter 1 provides a more detailed introduction to network algorithmics. For now, we informally define network algorithmics as an interdisciplinary systems approach to streamlining network implementations. Network algorithmics is *interdisciplinary*, because it requires techniques from diverse fields such as architecture, operating systems, hardware design, and algorithms. Network algorithmics is also a *systems* approach, because routers and servers are systems in which efficiencies can be gained by moving functions in time and space between subsystems.

In essence, this book is about three things: fundamental networking implementation bottlenecks, general principles to address new bottlenecks, and techniques for specific bottlenecks that can be derived from the general principles.

Fundamental bottlenecks for an endnode such as a PC or workstation include data copying, control transfer, demultiplexing, timers, buffer allocation, checksums, and protocol processing. Similarly, fundamental bottlenecks for interconnect devices such as routers and SAN switches include exact and prefix lookups, packet classification, switching, and the implementation of measurement and security primitives. Chapter 1 goes into more detail about the inherent causes of these bottlenecks.

The fundamental methods that encompass network algorithmics include implementation models (Chapter 2) and 15 implementation principles (Chapter 3). The implementation models include models of operating systems, protocols, hardware, and architecture. They are included because the world of network protocol implementation requires the skills of several different communities, including operating system experts, protocol pundits, hardware designers, and computer architects. The implementation models are an attempt to bridge the gaps between these traditionally separate communities.

On the other hand, the implementation principles are an attempt to abstract the main ideas behind many specific implementation techniques. They include such well-known principles as "Optimize the expected case." They also include somewhat less well-known principles, such as "Combine DRAM with SRAM," which is a surprisingly powerful principle for producing fast hardware designs for network devices.

While Part I of the book lays out the methodology of network algorithmics, Part II *applies* the methodology to specific network bottlenecks in endnodes and servers. For example, Part II discusses copy avoidance techniques (such as passing virtual memory pointers and RDMA) and efficient control transfer methods (such as bypassing the kernel, as in the VIA proposal, and techniques for building event-driven servers).

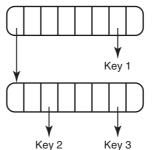

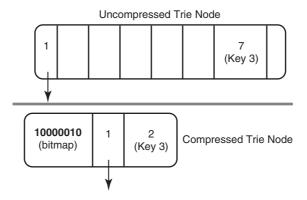

Similarly, Part III of the book applies the methodology of Part I to interconnect devices, such as network routers. For example, Part III discusses effficient prefix-lookup schemes (such as multibit or compressed tries) and efficient switching schemes (such as those based on virtual output queues and bipartite matching).

Finally, Part IV of the book applies the methodology of Part I to new functions for security and measurement that could be housed in either servers or interconnect devices. For example, Part IV discusses efficient methods to compress large traffic reports and efficient methods to detect attacks.

#### **ORGANIZATION OF THE BOOK**

This book is organized into four overall parts. Each part is made as self-contained as possible to allow detailed study. Readers that are pressed for time can consult the index or Table of Contents for a particular topic (e.g., IP lookups). More importantly, the opening section of

each chapter concludes with a Quick Reference Guide that points to the most important topics for implementors. The Quick Reference Guide may be the fastest guide for usefully skimming a chapter.

Part I of the book aims to familiarize the reader with the rules and philosophy of network algorithmics. It starts with Chapter 2, which describes simple models of protocols, operating systems, hardware design, and endnode and router architectures. Chapter 3 describes in detail the 15 principles used as a cornerstone for the book. Chapter 4 rounds out the first part by providing 15 examples, drawn for the most part from real implementation problems, to allow the reader a first opportunity to see the principles in action on real problems.

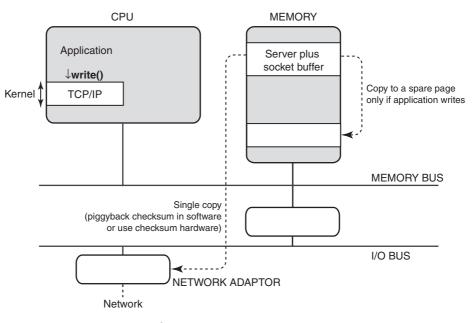

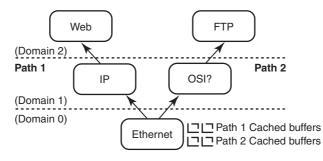

Part II of the book, called "Playing with Endnodes," shows how to build fast endnode implementations, such as Web servers, that run on general-purpose operating systems and standard computer architectures. It starts with Chapter 5, which shows how to reduce or avoid extra data copying. (Copying often occurs when network data is passed between implementation modules) and how to increase cache efficiency. Chapter 6 shows how to reduce or avoid the overhead of transferring control between implementation modules, such as the device driver, the kernel, and the application. Chapter 7 describes how to efficiently manage thousands of outstanding timers, a critical issue for large servers. Chapter 8 describes how to efficiently demultiplex data to receiving applications in a single step, allowing innovations such as user-level networking. Chapter 9 describes how to implement specific functions that often recur in specific protocol implementations, such as buffer allocation, checksums, sequence number bookkeeping, and reassembly. An overview of Part II can be found in Figure 1.1.

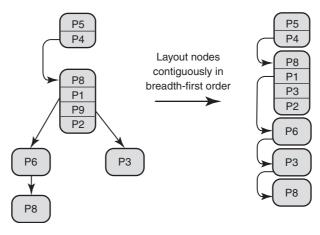

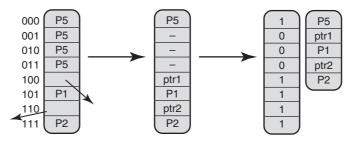

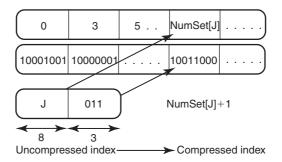

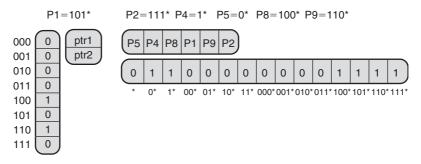

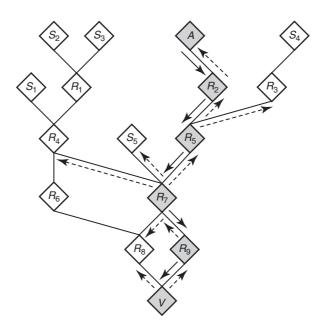

Part III of the book, called "Playing with Routers," shows how to build fast routers, bridges, and gateways. It begins with three chapters that describe state lookups of increasing complexity. Chapter 10 describes exact-match lookups, which are essential for the design of bridges and ARP caches. Chapter 11 describes prefix-match lookups, which are used by Internet routers to forward packets. Chapter 12 describes packet classification, a more sophisticated form of lookup required for security and quality of service. Chapter 13 describes how to build crossbar switches, which interconnect input and output links of devices such as routers. Finally, Chapter 14 describes packet-scheduling algorithms, which are used to provide quality-of-service, and Chapter 15 discusses routers as distributed systems, with examples focusing on performance and the use of design and reasoning techniques from distributed algorithms. While this list of functions seems short, one can build a fast router by designing a fast lookup algorithm, a fast switch, and fast packet-scheduling algorithms. Part IV, called "Endgame," starts by speculating on the potential need for implementing more complex tasks in the future. For example, Chapter 16 describes efficient implementation techniques for measurement primitives, while Chapter 17 describes efficient implementation techniques for security primitives. The book ends with a short chapter, Chapter 18, which reaches closure by distilling the unities that underly the many different topics in this book. This chapter also briefly presents examples of the use of algorithmics in a canonical router (the Cisco GSR) and a canonical server (the Flash Web server). A more detailed overview of Parts III and IV of the book can be found in Figure 1.2.

#### FEATURES

The book has the following features that readers, implementors, students, and instructors can take advantage of.

- *Intuitive introduction:* The introductory paragraph of each chapter in Parts II, III, and IV uses an intuitive, real-world analogy to motivate each bottleneck. For example, we use the analogy of making multiple photocopies of a document for data copying and the analogy of a flight database for prefix lookups.

- *Quick Reference Guide:* For readers familiar with a topic and pressed for time, the opening section of each chapter concludes with a Quick Reference Guide that points to the most important implementation ideas and the corresponding section numbers.

- *Chapter organization:* To help orient the reader, immediately after the Quick Reference Guide in each chapter is a map of the entire chapter.

- *Summary of techniques:* To emphasize the correlation between principles and techniques, at the start of each chapter is a table that summarizes the techniques described, together with the corresponding principles.

- *Consistent use of principles:* After a detailed description in Chapter 3 of 15 principles, the rest of the book consistently uses these principles in describing specific techniques. For reference, the principles are summarized inside the front cover. Principles are referred to consistently by number for example, **P9** for Principle 9. Since principle numbers are hard to remember, three aids are provided. Besides the inside front cover summary and the summary at the start of each chapter, the first use of a principle in any chapter is accompanied by an explicit statement of the principle.

- *Exercises:* Chapter 4 of the book provides a set of real-life examples of applying the principles that have been enjoyed by past attendees of tutorials on network algorithmics. Every subsequent chapter through Chapter 17 is followed by a set of exercises. Brief solutions to these exercises can be found in an instructor's manual obtainable from Morgan Kaufmann.

- *Slides:* Lecture slides in pdf for most chapters are available at Morgan Kaufmann's Web site www.mkp.com.

#### USAGE

This book can be used in many ways.

- *Textbook:* Students and instructors can use this book as the basis of a one-semester class. A semester class on network algorithmics can include most of Part I and can sample chapters from Part II (e.g., Chapter 5 on copying, Chapter 6 on control overhead) and from Part III (e.g., Chapter 11 on prefix lookups, Chapter 13 on switching).

- *Implementation guide:* Implementors who care about performance may wish to read all of Part I and then sample Parts II and III according to their needs.

- *Reference book:* Implementors and students can also use this book as a reference book in addition to other books on network protocols.

#### WHY THIS BOOK WAS WRITTEN

The impetus for this book came from my academic research into efficient protocol implementation. It also came from three networking products I worked on with colleagues: the first bridge, the Gigaswitch, and the Procket 40 Gbps router. To prove itself against detractors, the first bridge was designed to operate at wire speed, an idea that spread to routers and the entire industry. My experience watching the work of Mark Kempf on the first bridge (see Chapter 10) led to a lasting interest in speeding up networking devices.

Next, the DEC Gigaswitch introduced me to the world of switching. Finally, the Procket router was designed by an interdisciplinary team that included digital designers who had designed processors, experts who had written vast amounts of the software in core routers, and some people like myself who were interested in algorithms. Despite the varied backgrounds, the team produced innovative new ideas, which convinced me of the importance of interdisciplinary thinking for performance breakthroughs. This motivated the writing of Chapter 2 on implementation models, an attempt to bridge the gaps between the different communities involved in high-performance designs.

For several years, I taught a class that collected together these techniques. The 15 principles emerged as a way to break up the techniques more finely and systematically. In retrospect, some principles seem redundant and glib. However, they serve as part of a first attempt to organize a vast amount of material.

I have taught five classes and three tutorials based on the material in this book, and so this book has been greatly influenced by student responses and ideas.

#### ACKNOWLEDGMENTS

A special thanks to my editors: Karen Gettman and Rick Adams and Karyn Johnson; to all my advisors, who taught me so much: Wushow Chou, Arne Nillson, Baruch Awerbuch, Nancy Lynch; to all my mentors: Alan Kirby, Radia Perlman, Tony Lauck, Bob Thomas, Bob Simcoe, Jon Turner; to numerous colleages at DEC and other companies, especially to Sharad Merhotra, Bill Lynch, and Tony Li of Procket Networks, who taught me about real routers; to students who adventured in the field of network algorithmics with me; to numerous reviewers of this book and especially to Jon Snader, Tony Lauck, Brian Kernighan, Craig Partridge, and Radia Perlman for detailed comments; to Kevin D'Souza, Stefano Previdi, Anees Shaikh, and Darryl Veitch for their reviews and ideas; to my family, my mother, my wife's father and mother, and my sister; and, of course, to my wife, Aju, and my sons, Tim and Andrew.

I'd like to end by acknowledging my heroes: four teachers who have influenced me. The first is Leonard Bernstein, who taught me in his lectures on music that a teacher's enthusiasm for the material can be infectious. The second is George Polya, who taught me in his books on problem solving that the process of discovery is as important as the final discoveries themselves. The third is Socrates, who taught me through Plato that it is worth always questioning assumptions. The fourth is Jesus, who has taught me that life, and indeed this book, is not a matter of merit but of grace and gift.

## PART I

# The Rules of the Game

"Come, Watson, come!" he cried. "The game is afoot!"

-ARTHUR CONAN DOYLE IN The Abbey Grange

The first part of this book deals with specifying the rules of the network algorithmics game. We start with a quick introduction where we define network algorithmics and contrast it to algorithm design. Next, we present models of protocols, operating systems, processor architecture, and hardware design; these are the key disciplines used in the rest of the book. Then we present a set of 15 principles abstracted from the specific techniques presented later in the book. Part I ends with a set of sample problems together with solutions obtained using the principles. Implementors pressed for time should skim the Quick Reference Guides directly following the introduction to each chapter.

## CHAPTER 1

## Introducing Network Algorithmics

What really makes it an invention is that someone decides not to change the solution to a known problem, but to change the question.

—DEAN KAMEN

Just as the objective of chess is to checkmate the opponent and the objective of tennis is to win matches, the objective of the network algorithmics game is to battle networking implementation bottlenecks.

Beyond specific techniques, this book distills a fundamental way of crafting solutions to internet bottlenecks that we call *network algorithmics*. This provides the reader tools to design different implementations for specific contexts and to deal with new bottlenecks that will undoubtedly arise in the changing world of networks.

So what is network algorithmics? Network algorithmics goes beyond the design of efficient algorithms for networking tasks, though this has an important place. In particular, network algorithmics recognizes the primary importance of taking an interdisciplinary systems approach to streamlining network implementations.

Network algorithmics is an *interdisciplinary* approach because it encompasses such fields as architecture and operating systems (for speeding up servers), hardware design (for speeding up network devices such as routers), and algorithm design (for designing scalable algorithms). Network algorithmics is also a *systems* approach, because it is described in this book using a set of 15 principles that exploit the fact that routers and servers are systems, in which efficiencies can be gained by moving functions in time and space between subsystems.

The problems addressed by network algorithmics are fundamental networking performance *bottlenecks*. The solutions advocated by network algorithmics are a set of fundamental *techniques* to address these bottlenecks. Next, we provide a quick preview of both the bottlenecks and the methods.

#### **1.1 THE PROBLEM: NETWORK BOTTLENECKS**

The main problem considered in this book is how to make networks *easy to use* while at the same time realizing the *performance* of the raw hardware. Ease of use comes from the use of powerful network abstractions, such as socket interfaces and prefix-based forwarding. Unfortunately, without care such abstractions exact a large performance penalty when compared to the capacity of raw transmission links such as optical fiber. To study this performance gap

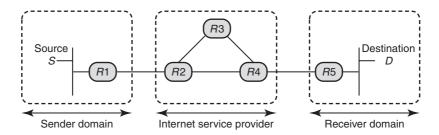

in more detail we examine two fundamental categories of networking devices, *endnodes* and *routers*.

#### 1.1.1 Endnode Bottlenecks

Endnodes are the endpoints of the network. They include personal computers and workstations as well as large servers that provide services. Endnodes are specialized toward computation, as opposed to networking, and are typically designed to support *general-purpose* computation. Thus endnode bottlenecks are typically the result of two forces: structure and scale.

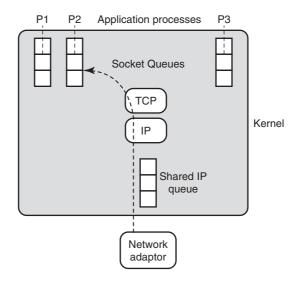

- *Structure:* To be able to run arbitrary code, personal computers and large servers typically have an operating system that mediates between applications and the hardware. To ease software development, most large operating systems are carefully structured as *layered software*; to protect the operating system from other applications, operating systems implement a set of *protection mechanisms*; finally, core operating systems routines, such as schedulers and allocators, are written using *general mechanisms* that target as wide a class of applications as possible. Unfortunately, the combination of layered software, protection mechanisms, and excessive generality can slow down networking software greatly, even with the fastest processors.

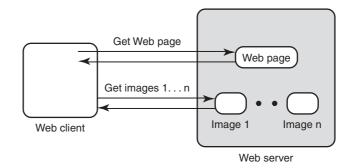

- *Scale:* The emergence of large servers providing Web and other services causes further performance problems. In particular, a large server such as a Web server will typically have thousands of concurrent clients. Many operating systems use inefficient data structures and algorithms that were designed for an era when the number of connections was small.

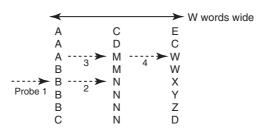

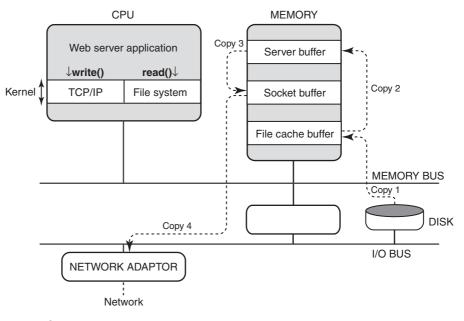

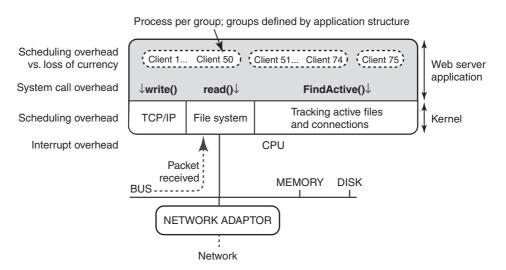

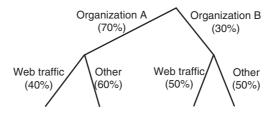

Figure 1.1 previews the main endnode bottlenecks covered in this book, together with causes and solutions. The first bottleneck occurs because conventional operating system structures cause packet data *copying* across protection domains; the situation is further complicated

| Bottleneck         | Chapter | Cause                                  | Sample Solution                                                  |

|--------------------|---------|----------------------------------------|------------------------------------------------------------------|

| Copying            | 5       | Protection, structure                  | Copying many data blocks without<br>OS intervention (e.g., RDMA) |

| Context switching  | 6       | Complex scheduling                     | User-level protocol implementations<br>Event-driven Web servers  |

| System calls       | 6       | Protection, structure                  | Direct channels from applications to drivers (e.g., VIA)         |

| Timers             | 7       | Scaling with number of timers          | Timing wheels                                                    |

| Demultiplexing     | 8       | Scaling with number of endpoints       | BPF and Pathfinder                                               |

| Checksums/<br>CRCs | 9       | Generality<br>Scaling with link speeds | Multibit computation                                             |

| Protocol<br>code   | 9       | Generality                             | Header prediction                                                |

FIGURE 1.1 Preview of endnode bottlenecks, solutions to which are described in Part II of the book.

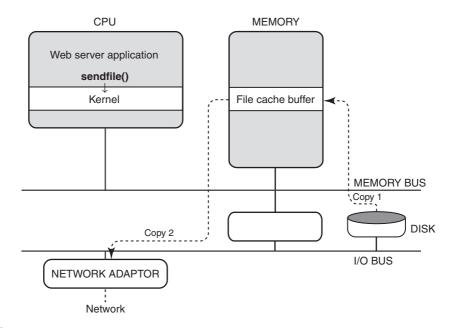

in Web servers by similar copying with respect to the file system and by other manipulations, such as checksums, that examine all the packet data. Chapter 5 describes a number of techniques to reduce these overheads while preserving the goals of system abstractions, such as protection and structure. The second major overhead is the *control overhead* caused by switching between threads of control (or protection domains) while processing a packet; this is addressed in Chapter 6.

Networking applications use timers to deal with failure. With a large number of connections the timer overhead at a server can become large; this overhead is addressed in Chapter 7. Similarly, network messages must be demultiplexed (i.e., steered) on receipt to the right end application; techniques to address this bottleneck are addressed in Chapter 8. Finally, there are several other common protocol processing tasks, such as buffer allocation and checksums, which are addressed in Chapter 9.

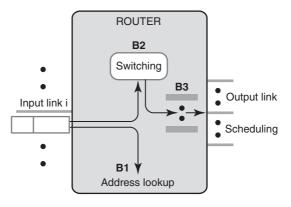

#### 1.1.2 Router Bottlenecks

Though we concentrate on Internet routers, almost all the techniques described in this book apply equally well to any other network devices, such as bridges, switches, gateways, monitors, and security appliances, and to protocols other than IP, such as FiberChannel.

Thus throughout the rest of the book, it is often useful to think of a *router* as a "generic network interconnection device." Unlike endnodes, these are special-purpose devices devoted to networking. Thus there is very little structural overhead within a router, with only the use of a very lightweight operating system and a clearly separated forwarding path that often is completely implemented in hardware. Instead of structure, the fundamental problems faced by routers are caused by *scale* and *services*.

- *Scale:* Network devices face two areas of scaling: *bandwidth scaling* and *population scaling*. Bandwidth scaling occurs because optical links keep getting faster, as the progress from 1-Gbps to 40-Gbps links shows, and because Internet traffic keeps growing due to a diverse set of new applications. Population scaling occurs because more endpoints get added to the Internet as more enterprises go online.

- *Services:* The need for speed and scale drove much of the networking industry in the 1980s and 1990s as more businesses went online (e.g., Amazon.com) and whole new online services were created (e.g., Ebay). But the very success of the Internet requires careful attention in the next decade to make it more effective by providing guarantees in terms of performance, security, and reliability. After all, if manufacturers (e.g., Dell) sell more online than by other channels, it is important to provide *network guarantees* delay in times of congestion, protection during attacks, and availability when failures occur. Finding ways to implement these new services at high speeds will be a major challenge for router vendors in the next decade.

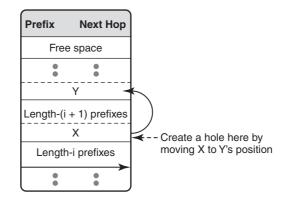

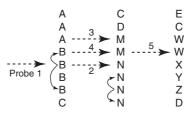

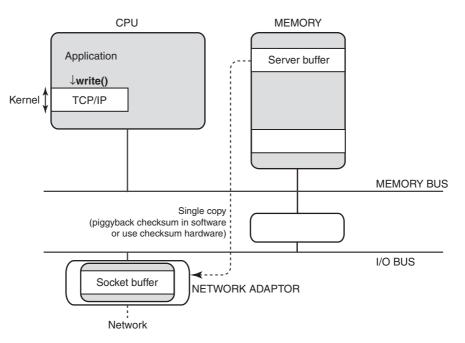

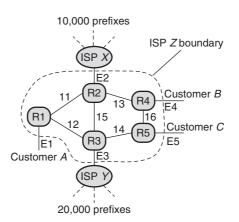

Figure 1.2 previews the main router (bridge/gateway) bottlenecks covered in this book, together with causes and solutions.

First, all networking devices forward packets to their destination by looking up a forwarding table. The simplest forwarding table lookup does an exact match with a destination address, as exemplified by bridges. Chapter 10 describes fast and scalable exact-match lookup schemes. Unfortunately, population scaling has made lookups far more complex for routers.

| Bottleneck            | Chapter | Cause                                                           | Sample Solution                                                           |

|-----------------------|---------|-----------------------------------------------------------------|---------------------------------------------------------------------------|

| Exact<br>lookups      | 10      | Link speed scaling                                              | Parallel hashing                                                          |

| Prefix<br>lookups     | 11      | Link speed scaling<br>Prefix database size scaling              | Compressed multibit tries                                                 |

| Packet classification | 12      | Service differentiation<br>Link speed and size scaling          | Decision tree algorithms<br>Hardware parallelism (CAMs)                   |

| Switching             | 13      | Optical-electronic speed gap<br>Head-of-line blocking           | Crossbar switches<br>Virtual output queues                                |

| Fair<br>queueing      | 14      | Service differentiation<br>Link speed scaling<br>Memory scaling | Weighted fair queueing<br>Deficit round robin<br>DiffServ, Core Stateless |

| Internal<br>bandwidth | 15      | Scaling of internal bus speeds                                  | Reliable striping                                                         |

| Measurement           | 16      | Link speed scaling                                              | Juniper's DCU                                                             |

| Security              | 17      | Scaling in number and intensity of attacks                      | Traceback with bloom filters<br>Extracting worm signatures                |

**FIGURE 1.2** Preview of router bottlenecks, solutions to which are described in Parts III and IV of the book.

To deal with large Internet populations, routers keep a single entry called a *prefix* (analogous to a telephone area code) for a large group of stations. Thus routers must do a more complex *longest-prefix-match* lookup. Chapter 11 describes solutions to this problem that scale to increasing speeds and table sizes.

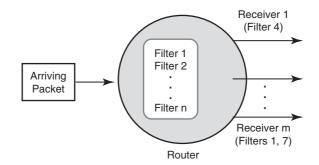

Many routers today offer what is sometimes called *service differentiation*, where different packets can be treated differently in order to provide service and security guarantees. Unfortunately, this requires an even more complex form of lookup called *packet classification*, in which the lookup is based on the destination, source, and even the services that a packet is providing. This challenging issue is tackled in Chapter 12.

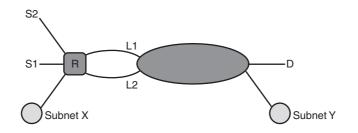

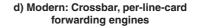

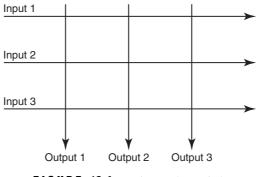

Next, all networking devices can be abstractly considered as switches that shunt packets coming in from a set of input links to a set of output links. Thus a fundamental issue is that of building a high-speed switch. This is hard, especially in the face of the growing gap between optical and electronic speeds. The standard solution is to use parallelism via a *crossbar switch*. Unfortunately, it is nontrivial to schedule a crossbar at high speeds, and parallelism is limited by a phenomenon known as *head-of-line blocking*. Worse, population scaling and optical multiplexing are forcing switch vendors to build switches with a large number of ports (e.g., 256), which exacerbates these other problems. Solutions to these problems are described in Chapter 13.

While the previous bottlenecks are caused by scaling, the next bottleneck is caused by the need for new services. The issue of providing performance guarantees at high speeds is treated in Chapter 14, where the issue of implementing so-called QoS (quality of service) mechanisms is studied. Chapter 15 briefly surveys another bottleneck that is becoming an increasing problem: the issue of bandwidth within a router. It describes sample techniques, such as striping across internal buses and chip-to-chip links.

The final sections of the book take a brief look at emerging services that must, we believe, be part of a well-engineered Internet of the future. First, routers of the future must build in support for measurement, because measurement is key to engineering networks to provide guarantees. While routers today provide some support for measurement in terms of counters and NetFlow records, Chapter 16 also considers more innovative measurement mechanisms that may be implemented in the future.

Chapter 17 describes security support, some of which is already being built into routers. Given the increased sophistication, virulence, and rate of network attacks, we believe that implementing security features in networking devices (whether routers or dedicated intrusion prevention/detection devices) will be essential. Further, unless the security device can keep up with high-speed links, the device may miss vital information required to spot an attack.

#### **1.2 THE TECHNIQUES: NETWORK ALGORITHMICS**

Throughout this book, we will talk of many specific techniques: of interrupts, copies, and timing wheels; of Pathfinder and Sting; of why some routers are very slow; and whether Web servers can scale. But what underlies the assorted techniques in this book and makes it more than a recipe book is the notion of *network algorithmics*. As said earlier, network algorithmics recognizes the primary importance of taking a *systems* approach to streamlining network implementations.

While everyone recognizes that the Internet is a system consisting of routers and links, it is perhaps less obvious that every networking device, from the Cisco GSR to an Apache Web server, is also a system. A system is built out of interconnected subsystems that are instantiated at various points in time. For example, a core router consists of line cards with forwarding engines and packet memories connected by a crossbar switch. The router behavior is affected by decisions at various time scales, which range from manufacturing time (when default parameters are stored in NVRAM) to route computation time (when routers conspire to compute routes) to packet-forwarding time (when packets are sent to adjoining routers).

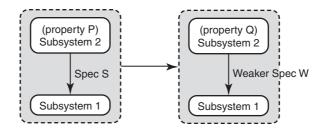

Thus one key observation in the systems approach is that one can often design an efficient subsystem by moving some of its functions in *space* (i.e., to other subsystems) or in *time* (i.e., to points in time before or after the function is apparently required). In some sense, the practitioner of network algorithmics is an unscrupulous opportunist willing to change the rules at any time to make the game easier. The only constraint is that the functions provided by the overall system continue to satisfy users.

In one of Mark Twain's books, a Connecticut Yankee is transported back in time to King Arthur's court. The Yankee then uses a gun to fight against dueling knights accustomed to jousting with lances. This is an example of changing system assumptions (replacing lances by guns) to solve a problem (winning a duel).

Considering the constraints faced by the network implementor at high speeds — increasingly complex tasks, larger systems to support, small amounts of high-speed memory, and a small number of memory accesses — it may require every trick, every gun in one's arsenal, to keep pace with the increasing speed and scale of the Internet. The designer can throw hardware at the problem, change the system assumptions, design a new algorithm — whatever it takes to get the job done.

This book is divided into four parts. The first part, of which this is the first chapter, lays a foundation for applying network algorithmics to packet processing. The second chapter of the first part outlines models, and the third chapter presents general principles used in the remainder of the book.

One of the best ways to get a quick idea about what network algorithmics is about is to plunge right away into a warm-up example. While the warm-up example that follows is in the context of a device within the network where new hardware can be designed, note that Part 2 is about building efficient servers using only software design techniques.

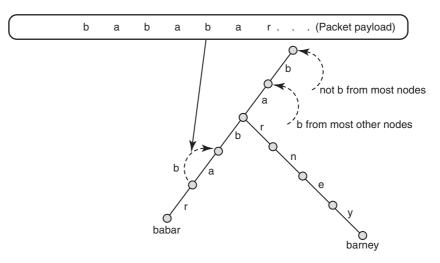

#### 1.2.1 Warm-up Example: Scenting an Evil Packet

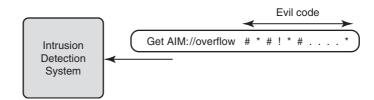

Imagine a front-end network monitor (or intrusion detection system) on the periphery of a corporate network that wishes to flag suspicious incoming packets — packets that could contain attacks on internal computers. A common such attack is a *buffer overflow* attack, where the attacker places machine code C in a network header field F.

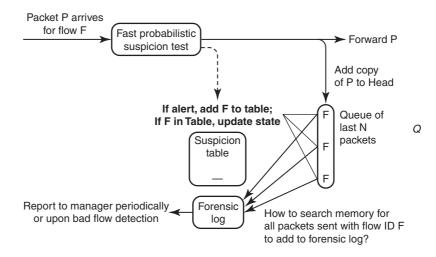

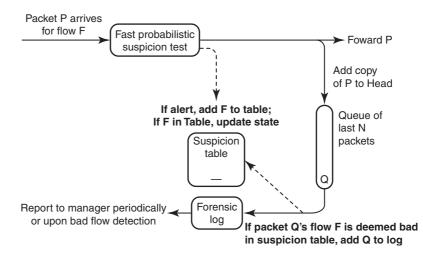

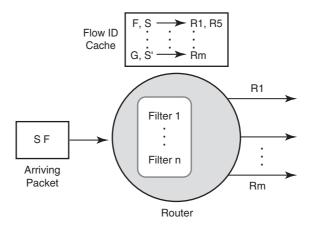

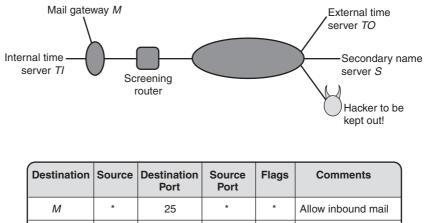

If the receiving computer allocates a buffer too small for header field F and is careless about checking for overflow, the code C can spill onto the receiving machine's stack. With a little more effort, the intruder can make the receiving machine actually execute evil code C. C then takes over the receiver machine. Figure 1.3 shows such an attack embodied in a familiar field, a destination Web URL (uniform resource locator). How might the monitor detect the presence of such a suspicious URL? A possible way is to observe that URLs containing evil code are often too long (an easy check) and often have a large fraction of unusual (at least in URLs) characters, such as #. Thus the monitor could mark such packets (containing URLs that are too long and have too many occurrences of such unusual characters) for more thorough examination.

It is worth stating at the outset that the security implications of this strategy need to be carefully thought out. For example, there may be several innocuous programs, such as CGI scripts, in URLs that lead to false positives. Without getting too hung up in overall architectural implications, let us assume that this was a specification handed down to a chip architect by a security architect. We now use this sample problem, suggested by Mike Fisk, to illustrate algorithmics in action.

Faced with such a specification, a chip designer may use the following design process, which illustrates some of the principles of network algorithmics. The process starts with a strawman design and refines the design using techniques such as designing a better algorithm, relaxing the specification, and exploiting hardware.

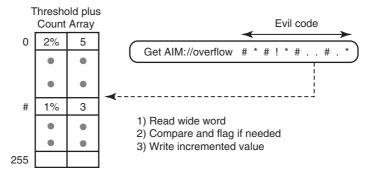

**FIGURE 1.3** Getting wind of an evil packet by noticing the frequency of unprintable characters.

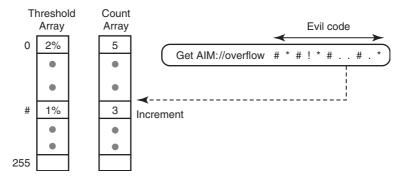

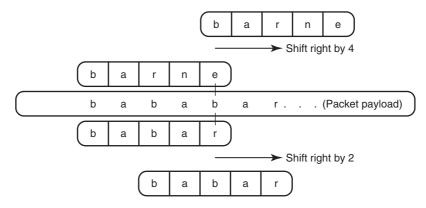

**FIGURE 1.4** Strawman solution for detecting an evil packet by counting occurrences of each character via a count array (middle) and then comparing in a final pass with an array of acceptable thresholds (left).

#### 1.2.2 Strawman Solution

The check of overall length is straightforward to implement, so we concentrate on checking for a prevalence of suspicious characters. The first strawman solution is illustrated in Figure 1.4. The chip maintains two arrays, T and C, with 256 elements each, one for each possible value of an 8-bit character. The threshold array, T, contains the acceptable percentage (as a fraction of the entire URL length) for each character. If the occurrences of a character in an actual URL fall above this fraction, the packet should be flagged. Each character can have a different threshold.

The count array, C, in the middle, contains the current count C[i] for each possible character i. When the chip reads a new character "i" in the URL, it increments C[i] by 1. C[i] is initialized to 0 for all values of i when a new packet is encountered. The incrementing process starts only after the chip parses the HTTP header and recognizes the start of a URL.

In HTTP, the end of a URL is signified by two newline characters; thus one can tell the length of the URL only after parsing the entire URL string. Thus, after the end of the URL is encountered, the chip makes a final pass over the array C. If  $C[j] \ge L \cdot T[j]$  for any j, where L is the length of the URL, the packet is flagged.

Assume that packets are coming into the monitor at high speed and that we wish to finish processing a packet before the next one arrives. This requirement, called *wire speed processing*, is very common in networking; it prevents processing backlogs even in the worst case. To meet wire speed requirements, ideally the chip should do a small constant number of operations for every URL byte. Assume the main step of incrementing a counter can be done in the time to receive a byte.

Unfortunately, the two passes over the array, first to initialize it and then to check for threshold violations, make this design slow. Minimum packet sizes are often as small as 40 bytes and include only network headers. Adding 768 more operations (1 write and 1 read to each element of C, and 1 read of T for each of 256 indices) can make this design infeasible.

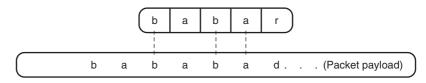

#### 1.2.3 Thinking Algorithmically

Intuitively, the second pass through the arrays *C* and *T* at the end seems like a waste. For example, it suffices to alarm if *any* character is over the threshold. So why check all characters?

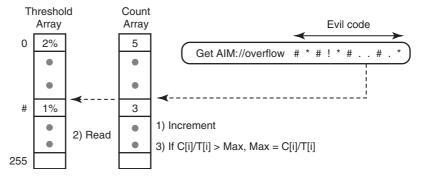

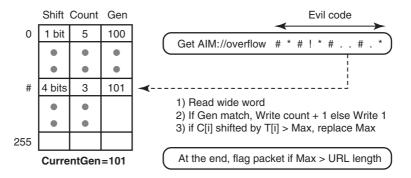

**FIGURE 1.5** Avoiding the final loop through the threshold array by keeping track only of *Max*, the highest counter encountered so far relative to its threshold value.

This suggests keeping track only of the largest character count c; at the end perhaps the algorithm needs to check only whether c is over threshold with respect to the total URL length L.

This does not quite work. A nonsuspicious character such as "e" may well have a very high occurrence count. However, "e" is also likely to be specified with a high threshold. Thus if we keep track only of "e" with, say, a count of 20, we may not keep track of "#" with, say, a count of 10. If the threshold of "#" is much smaller, the algorithm may cause a *false negative*: The chip may fail to alarm on a packet that should be flagged.

The counterexample suggests the following fix. The chip keeps track in a register of the highest counter relativized to the threshold value. More precisely, the chip keeps track of the highest relativized counter *Max* corresponding to some character *k*, such that C[k]/T[k] = Max is the highest among all characters encountered so far. If a new character *i* is read, the chip increments C[i]. If C[i]/T[i] > Max, then the chip replaces the current stored value of *Max* with C[i]/T[i]. At the end of URL processing, the chip alarms if  $Max \ge L$ .

Here's why this works. If  $Max = C[k]/T[k] \ge L$ , clearly the packet must be flagged, because character k is over threshold. On the other hand, if C[k]/T[k] < L, then for any character i, it follows that  $C[i]/T[i] \le C[k]/T[k] < L$ . Thus if Max falls below threshold, then no character is above threshold. Thus there can be no false negatives. This solution is shown in Figure 1.5.

#### 1.2.4 Refining the Algorithm: Exploiting Hardware

The new algorithm has eliminated the loop at the end but still has to deal with a divide operation while processing each byte. Divide logic is somewhat complicated and worth avoiding if possible — but how?

Returning to the specification and its intended use, it seems likely that thresholds are not meant to be exact floating point numbers. It is unlikely that the architect providing thresholds can estimate the values precisely; one is likely to approximate 2.78% as 3% without causing much difference to the security goals. So why not go further and approximate the threshold by some power of 2 less than the exact intended threshold? Thus if the threshold is 1/29, why not approximate it as 1/32?

**FIGURE 1.6** Using a wide word and a coalesced array to combine 2 reads into one.

Changing the specification in this way requires negotiation with the system architect. Assume that the architect agrees to this new proposal. Then a threshold such as 1/32 can be encoded compactly as the corresponding power of 2 — i.e., 5. This threshold *shift* value can be stored in the threshold array instead of a fraction.

Thus when a character *j* is encountered, the chip increments C[j] as usual and then shifts C[j] to the left — dividing by 1/x is the same as multiplying by x — by the specified threshold. If the shifted value is higher than the last stored value for *Max*, the chip replaces the old value with the new value and marches on.

Thus the logic required to implement the processing of a byte is a simple shift-andcompare. The stored state is only a single register to store *Max*. As it stands, however, the design requires a Read to the Threshold array (to read the shift value), a Read to the Count array (to read the old count), and a Write to the Count array (to write back the incremented value).

Now reads to memory — 1-2 nsec even for the fastest on-chip memories but possibly even as slow as 10 nsec for slower memories — are slower than logic. Single gate delays are only in the order of picoseconds, and shift logic does not require too many gate delays. Thus the processing bottleneck is the number of memory accesses.

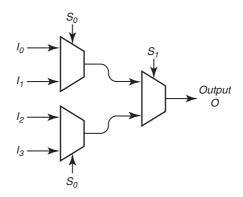

The chip implementation can combine the 2 Reads to memory into 1 Read by coalescing the Count and Threshold arrays into a single array, as shown in Figure 1.6. The idea is to make the memory words wide enough to hold the counter (say, 15 bits to handle packets of length 32K) and the threshold (depending on the precision necessary, no more than 14 bits). Thus the two fields can easily be combined into a larger word of size 29 bits. In practice, hardware can handle much larger words sizes of up to 1000 bits. Also, note that extracting the two fields packed into a single word, quite a chore in software, is trivial in hardware by routing wires appropriately between registers or by using multiplexers.

#### 1.2.5 Cleaning Up

We have postponed one thorny issue to this point. The terminal loop has been eliminated while leaving the initial initialization loop. To handle this, note that the chip has spare time for initialization after parsing the URL of the current packet and before encountering the URL of the next packet.

Unfortunately, packets can be as small as 50 bytes, even with an HTTP header. Thus even assuming a slack of 40 non-URL bytes other than the 10 bytes of the URL, this still does not suffice to initialize a 256-byte array without paying 256/40 = 6 more operations per byte than during the processing of a URL. As in the URL processing loop, each initialization step requires a Read and Write of some element of the coalesced array.

A trick among lazy people is to postpone work until it is absolutely needed, in the hope that it may never be needed. Note that, strictly speaking, the chip need not initialize a C[i] until character *i* is accessed for the first time in a subsequent packet. But how can the chip tell that it is seeing character *i* for the first time?

To implement lazy evaluation, each memory word representing an entry in the coalesced array must be expanded to include, say, a 3-bit generation number G[i]. The generation number can be thought of as a value of clock time measured in terms of packets encountered so far, except that it is limited to 3 bits. Thus, the chip keeps an additional register g, besides the extra G[i] for each i, that is 3 bits long; g is incremented mod 8 for every packet encountered. In addition, every time C[i] is updated, the chip updates G[i] as well to reflect the current value of g.

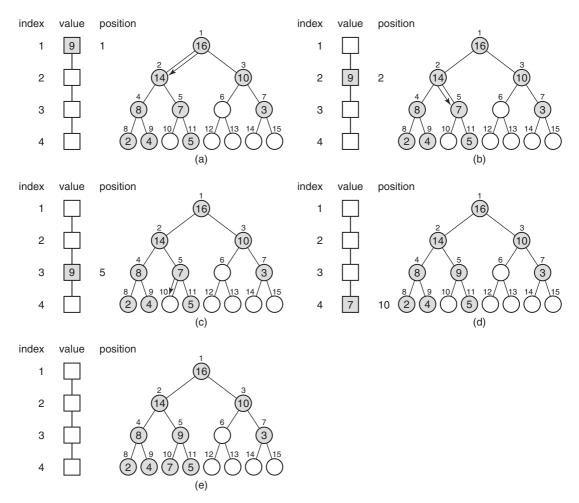

Given the generation numbers, the chip need not initialize the count array after the current packet has been processed. However, consider the case of a packet whose generation number is h, which contains a character i in its URL. When the chip encounters i while processing the packet the chip reads C[i] and G[i] from the Count array. If  $G[i] \neq h$ , this clearly indicates that entry i was last accessed by an earlier packet and has not been subsequently initialized. Thus the logic will write back the value of C[i] as 1 (initialization plus increment) and set G[i] to h. This is shown in Figure 1.7.

The careful reader will immediately object. Since the generation number is only 3 bits, once the value of g wraps around, there can be aliasing. Thus if G[i] is 5 and entry i is not accessed until eight more packets have gone by, g will have wrapped around to 5. If the next packet contains i, C[i] will not be initialized and the count will (wrongly) accumulate the count of i in the current packet together with the count that occurred eight packets in the past.

The chip can avoid such aliasing by doing a separate "scrubbing" loop that reads the array and initializes all counters with outdated generation numbers. For correctness, the chip must guarantee one complete scan through the array for every eight packets processed. Given that one has a slack of (say) 40 non-URL bytes per packet, this guarantees a slack of 320 non-URL

FIGURE 1.7 The final solution with generation numbers to finesse an initialization loop.